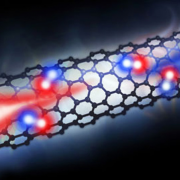

人工智能(AI)目前正经历着由深度学习(DL)技术驱动的蓬勃发展阶段,该技术依赖于并行运行连接的简单计算单元网络。在传统的冯·诺依曼机器中,存储器和处理单元之间的低通信带宽不支持广泛依赖于大数据集的新兴应用的要求。最近的计算范式,如高并行化和近内存计算,在一定程度上有助于缓解数据通信瓶颈,但需要范式转换的概念。忆阻器是一种超越互补金属氧化物半导体(CMOS)技术的新型技术,由于其独特的内在器件特性,使存储和计算能够在低功耗下以小模型大规模的并行占用空间,因此是存储设备的一个很有前景的选择。从理论上讲,这直接转化为能源效率和计算吞吐量的大幅提高,但仍存在各种实际挑战。鉴于此,来自阿卜杜拉国王科技大学的Mario Lanza研究实现了基于硬件的忆阻人工神经网络(ANNs)的最新成果。

文章要点:

1) 该研究详细描述了忆阻器每个模块的工作原理和不同的设计方案及其各自的优缺点,以及准确估计性能指标所需的工具;

2) 此外,该研究为那些打算开始在该领域工作的人和寻求整体方法的专家提供了一份关于忆阻神经网络所涉及的材料和方法的全面协议。

参考资料:

Aguirre, F., Sebastian, A., Le Gallo, M. et al. Hardware implementation of memristor-based artificial neural networks. Nat. Commun. (2024).

10.1038/s41467-024-45670-9

https://doi.org/10.1038/s41467-024-45670-9