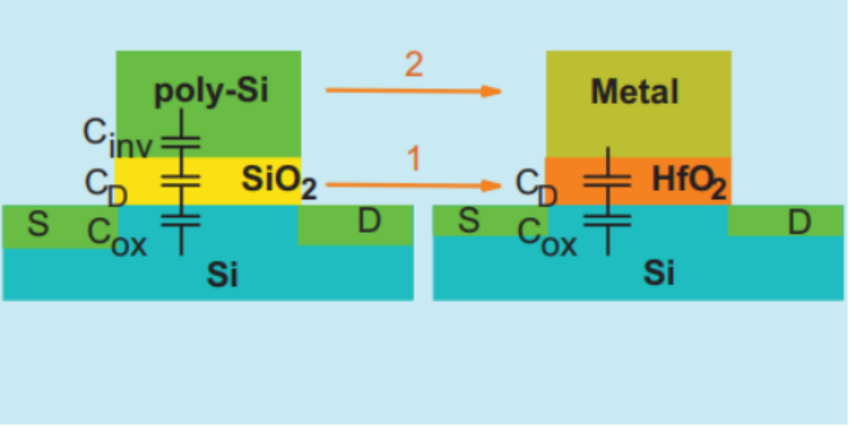

自1947年贝尔实验室的John Baden等人研发出了第一个功能点接触锗晶体管以来,晶体管就依靠重量轻,可大量小型化生产等优点快速取代真空管,成为电子半导体行业的宠儿,随后晶体管呈现爆发式发展,并且逐渐演变出i)互补金属氧化物半导体(CMOS)晶体管(尺寸25~32 nm)、ii)鳍式场效应(FinFET)晶体管(尺寸~7 nm)以及iii)全能门(GAA)FinFET技术的晶体管(尺寸~3 nm)等类型的晶体管。其中CMOS晶体管的规模化应用需求(如:小型化、低能耗等)导致其中SiO2层栅极变得非常薄,以至于栅极泄漏电流变得太大、迁移率下降,导致短沟道中的高电场、穿通效应等问题,极大限制了其应用前景。因此,提高栅极至沟道的电容以保持对栅极电极对沟道的控制并降低工作电压是完善CMOS晶体管发展的重要途径,而受量子隧穿效应的限制,SiO2半导体中等效氧化层厚度极限小值约为16 Å,无法再继续降低厚度,因此,更换 i)高介电常数的材料(如HfO2介电层取代SiO2介电层)以进一步提高栅极氧化物电容是重要的解决办法之一;另外,晶体管上的多晶硅的耗尽效应以及由阈值电压钉扎效应带来的多晶硅栅极-栅极氧化物不兼容的问题也呈需解决,而ii)使用金属栅极则可以很好的解决上述问题。

图1:用高介电常数栅极氧化物和金属栅极替代SiO2栅极氧化物和多晶硅栅极的示意图。(Reference: High-K materials and metal gates for CMOS applications )

目前,为进一步深入挖掘晶体管的潜力,栅极氧化物通常被设计成两层的组合。第一层是通过自限制工艺形成的界面SiO2层(8.0 - 8.5 Å),然后是高介电的HfO2层(~20 Å),这种串联的模式下的高电容有利于抑制短沟道效应,但等效氧化层厚度仍只能达到~9.5 Å(HfO2),为了继续降低这一值,半导体行业实施了复杂的清除技术以在全栅堆叠沉积后减少SiO2的厚度,但较薄的SiO2层又会导致电子泄漏、迁移率下降和可靠性等问题。

核心内容

基于此,加州大学伯克利分校Suraj S. Cheemay、Nirmaan Shanker等人利用混合铁电-反铁电(FE-AFE)的去极化效应与特殊堆叠效果,提出了一种20 Å稳定厚度的超薄HfO2-ZrO2超晶格栅叠层。其金属-氧化物-半导体电容器的总等效氧化物厚度相当于~6.5 Å的有效厚度的SiO2,媲美目前先进的晶体管。

铁电-反铁电(FE-AFE)效应去极化增大电容

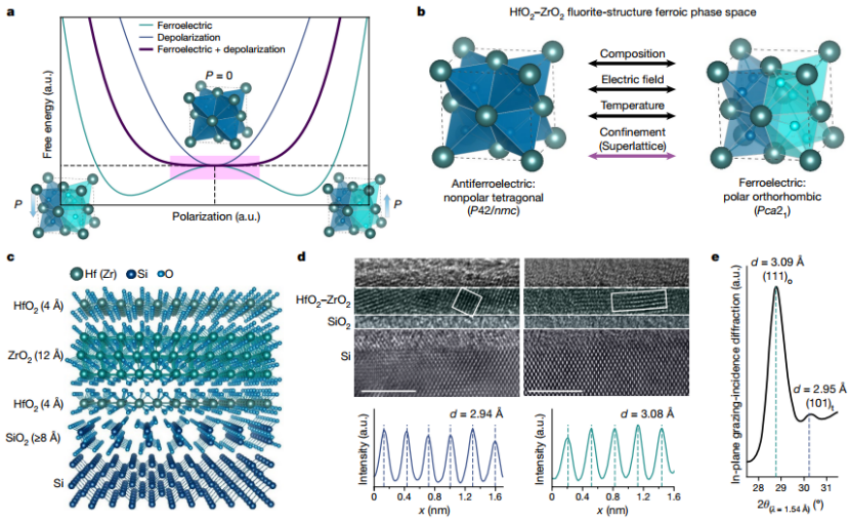

HfO2–ZrO2薄膜是使用原子层沉积生长的,通过大量表征证实了Hf 4 Å–Zr 12 Å周期性,且结构中存在FE(正交相,Pca21)-AFE(四方相,P42/nmc)结构。稳定厚度的20 Å的二元氧化物薄膜中(HfO2–ZrO2–HfO2(HZH))的混合非极性-极性结构相竞争会提高其介电常数:i)在低电场下,FE-AFE会在FE层上产生去极化场,HZH薄膜异质结构中非极性-极性相则通过去极化场使FE层能量拉平,系统中的非均匀弹性能量则会进一步破坏长程极化,抑制极化,实现去极化的目的。此外,ii)偏振沿着Pca21正交结构的主晶格方向定向投影会引入额外的去偏振场,其与非极性AFE相静电耦合,这种不均匀性也会诱导去极化场和增强敏感性。相较于相同厚度的传统AFE ZrO2和FE Zr/HfO2,去极化的HZH薄膜介电常数(52)明显增大,总电容也相应的增大。

图2:超薄HfO2–ZrO2中负电容的原子级设计

堆叠结构引起的电容增大

在金属-氧化物-半导体(MOS)电容器结构的硅衬底上生长超晶格以评估其等效氧化层厚度。与仅将界面SiO2置于Si顶部相比,超晶格叠层展示了更大的存储电荷能力。HZH极化-电场的负斜率关系也表现出负电容稳定性。

与具有相同20 Å厚度的其他传统叠层(电介质HfO2、AFE ZrO2、FE Zr:HfO2)相比,超晶格叠层的累积显示出更大的电容。与具有相同厚度金属双层(Hf:Zr 8:12)和固溶体(Hf:Zr [2:3]4)相比,Hf:Zr:Hf(4:12:4)三层表现出强电容。另外,由于在固溶体中会存在同形变相边界(MPB),其会改变组成元素的体积分数,引起电容变化,而对于超薄HZH多层膜到底是由于MPB结构引起的容量变化还是特殊堆叠的超晶格结构呢?超薄HZH多层膜中极性FE相的负自由能曲率补偿了非极性AFE相的正曲率而导致能量分布趋于平坦则说明了电容改变是由原子级HfO2-ZrO2层的堆叠决定的,而不是由组成元素的体积分数决定的。通过对比MPB效应的电容,也均小于本研究的电容,这表明HZH薄膜中的增强电容不是简单地由掺杂驱动,而是可以通过多层结构的配置来调整。在超薄状态下,表面能成为确定多晶相稳定性的更主要考虑因素。因此,该研究中堆叠的重要性被放大了。

图3:超薄HfO2-ZrO2混合铁质结构中的增强电容

实用性考察

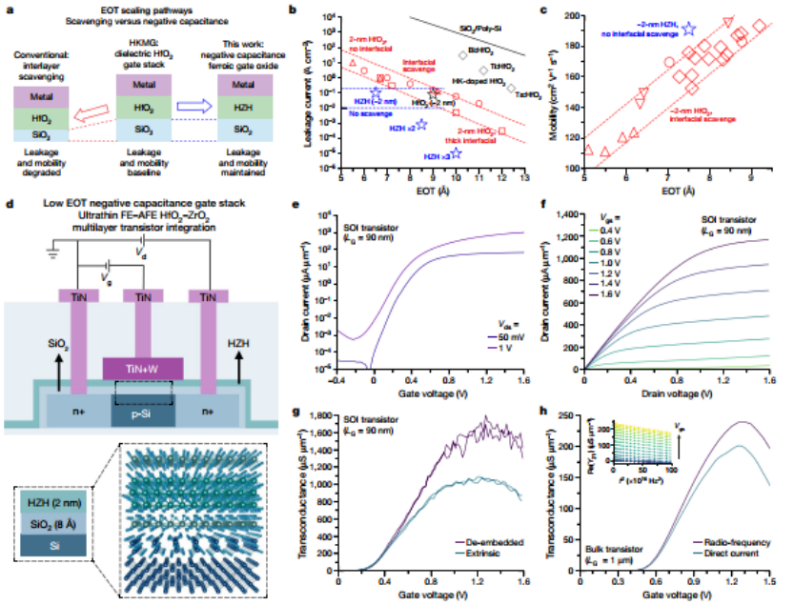

晶体管的漏电流、迁移率均与等效氧化层厚度(EOT)相关,相比其他栅格叠层,HZH叠层的漏电流在相同EOT下显著降低,这主要是因为:在9 Å以下,其他栅格叠层需要复杂的清除技术来降低界面SiO2的厚度。而HZH叠层在~6.5 Å仍不需要清除,从而维持较低的漏电流。界面SiO2的清除还会影响迁移率的损失,与降低传统的高介电栅极堆叠EOT导致的迁移率下降想比,低于9 Å EOT的HZH迁移率没有损失,这表明HZH堆叠具有优异的电子传输能力(迁移率损失小)。i)从集成2-nm HZH异质结构栅堆叠的长沟道晶体管中提取的原始迁移率也超过了行业报告的值,在2-nm HZH异质结构栅堆叠的长沟道晶体管上检查了高频条件电容响应,射频结果表明观察到的电容增强不限于低频范围,在高频下也成立;ii)在18 nm 厚度的绝缘体上硅晶体管上制造的较短通道器件以测量过驱动电压下漏电流响应,结果表明过电压1 V下漏电流为1 mA μm-1;iii)低EOT不会对电子传输产生不利影响;iv)随着应力时间的增加,平带电压偏移和电容退化可以忽略不计,表明了该晶体管的可靠性,以前研究则HZH叠层可以显著提高器件性能,具有实用性。

图4:使用超薄混合铁基HfO2–ZrO2栅叠层提高器件性能

小结

综上所述,该研究表明,超薄HZH多层膜在2 nm厚度范围内利用铁电-反铁电(FE-AFE)效应显著提高了负电容介导的电容增强,确立了原子层堆叠的关键作用,将EOT降低到传统上需要仔细清除界面SiO2的阈值以下,显著降低了漏电流与维持了迁移率,为电子器件中超越传统HfO2基高介电常数材料的先进栅极氧化物叠层的设计提供了思路。

参考文献:

Suraj S. Cheema, Nirmaan Shanker, Li-Chen Wang et al. Ultrathin ferroic HfO2–ZrO2 superlattice gate stack for advanced transistors. Nature 604, 65–71(2022). https://www.nature.com/articles/s41586-022-04425-6

John Robertson, Robert M. Wallace et al. High-K materials and metal gates for CMOS applications. Materials Science and Engineering R 88, 1–41(2015). https://www.sciencedirect.com/science/article/pii/S0927796X14001168