集成电路芯片主要利用电子的电荷自由度来实现信息的传输和处理,基于电荷自由度的电流,服从焦耳定律,电流的流动会产生焦耳热,从而产生不可避免的热功耗。因此,需要探索利用其他电子自由度来制备电子器件,减小或消除芯片工作时候的焦耳热。“能谷”是材料能带结构中能量-动量色散关系中的极值点。能谷是电子的一种自由度,可以像电荷或自旋一样作为信息载流子(如实现“开”和“关”易失计算或“0”和“1”非易失存储),对低能声子散射不敏感。谷电子通常采用光学方法来激发,长程库仑相互作用导致激子谷极化通常具有较短的寿命(皮秒),很难在室温下操作能谷。因此,目前利用能谷机制实现室温晶体管器件是一个较大的挑战。

理论上,基于手征反常效应和贝里曲率的能谷输运可以实现下百微米尺度的输运;实验中,基于拓扑半金属Cd3As2制备的器件,可以在室温测得微米级的谷扩散特征长度。然而,由于拓扑半金属的费米能级比较难用静电栅压来调节,通过调节贝里曲率强度从而实现器件的“开”和“关”态很困难。近年的研究工作,发现了一种新型拓扑材料碲烯 (Te)。这种材料具有半导体性能带结构,且外尔点离能带的极值点比较近。与拓扑半金属相比,静电栅压更能有效调控外尔半导体Te的费米能级和贝里曲率强度。基于外尔半导体Te,我们的谷晶体管实现了105 的开/关比(易失性),并且实现了32 种稳定的非易失性状态。在人工神经网络的推理过程中,功耗值仅为~ fW 的能谷贡献和~pW的欧姆贡献,展示出谷晶体管在低功耗神经形态计算中的应用潜力。

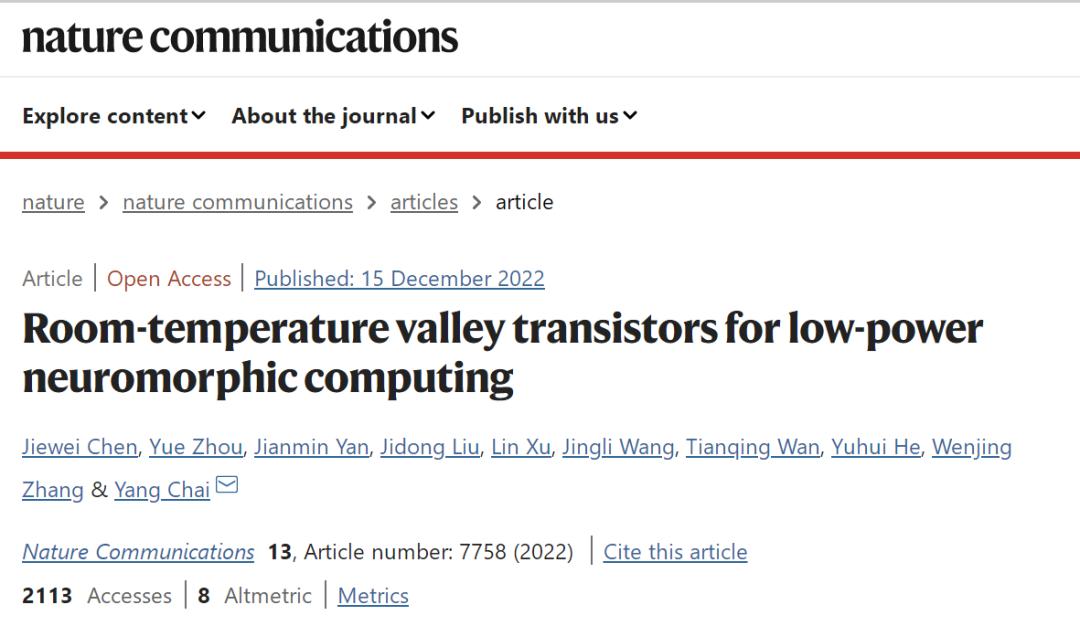

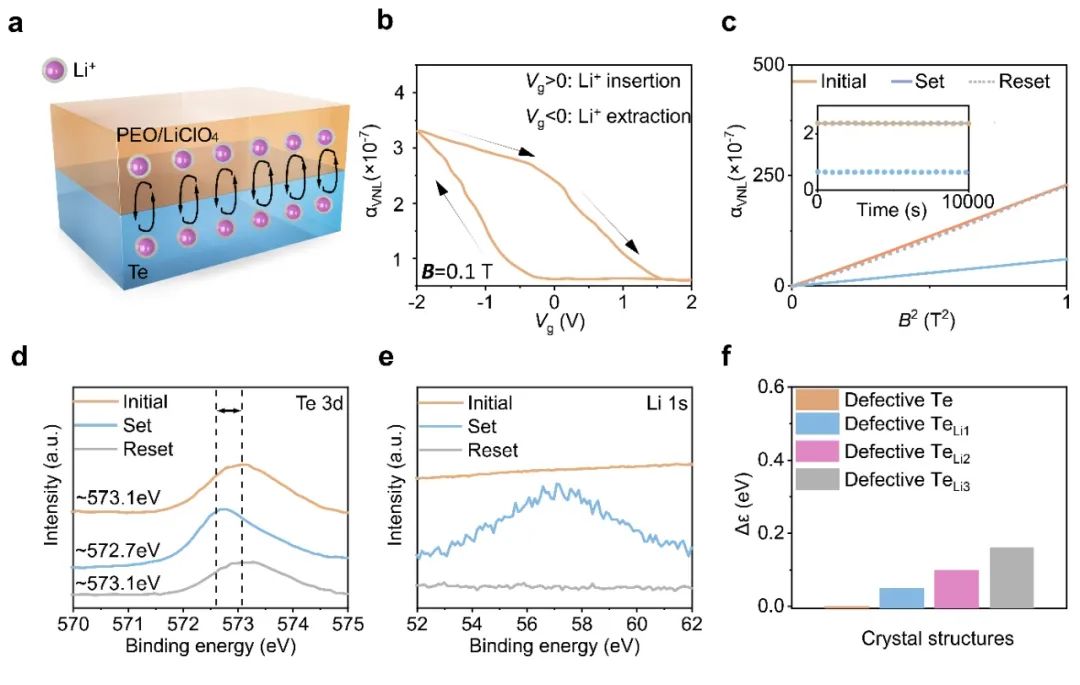

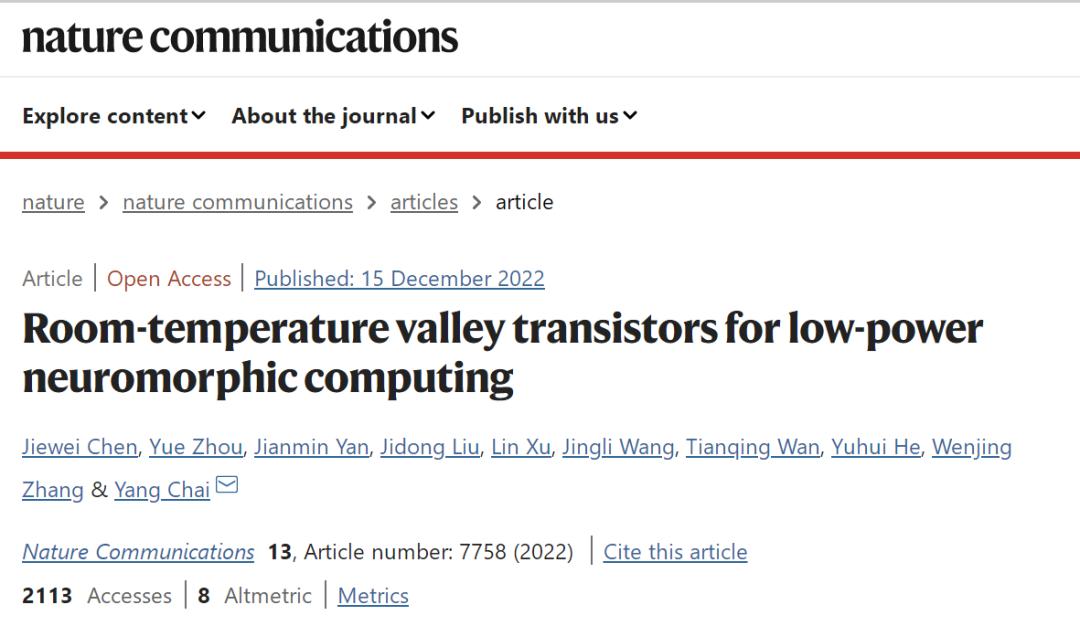

外尔材料的拓扑性质源自非平凡的贝里曲率。图1a中的箭头显示了贝里曲率从一个外尔点(W+,浅棕色)到另一个(W-,蓝色)的通量。非局域结构(图1b)可以显著减少传统欧姆输运的影响,允许产生、传播(红色箭头)、检测和调制谷输运。基于非平庸贝里曲率,在平行磁场和电场下产生不平衡谷极化(图1c)。谷间散射决定了传播期间谷的寿命,这需要较大的动量转移(图1d)。理论上,谷可以达到100微米的特征输运长度。我们可以通过调节费米能级和贝里曲率来控制谷输运强度(图1e)。当费米能级靠近外尔点时,贝里曲率很强,可以产生很强的谷信号;当费米能级远离外尔点时,贝里曲率很弱,器件输出很弱的谷信号。因此,我们可以通过静电栅压来控制费米能级的位置的方式来场效应晶体管。

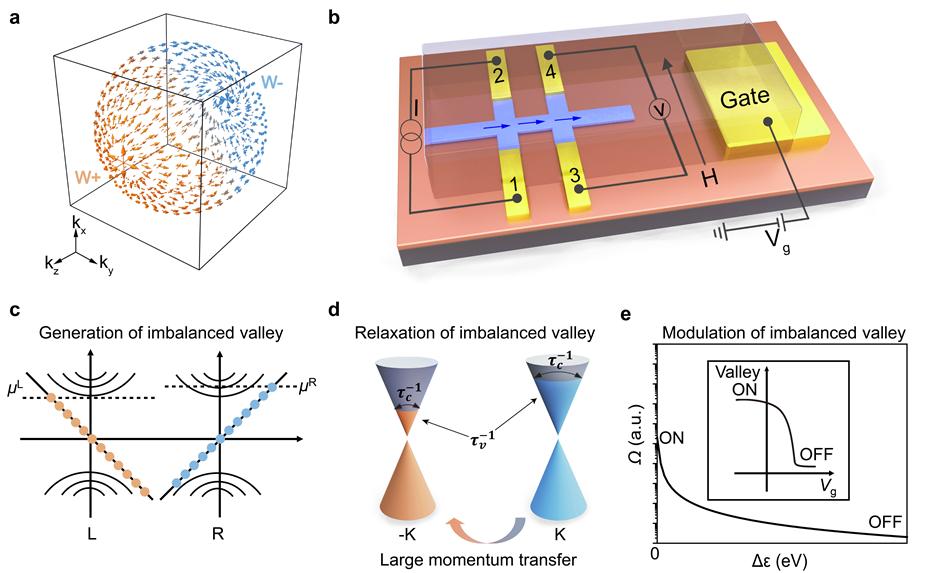

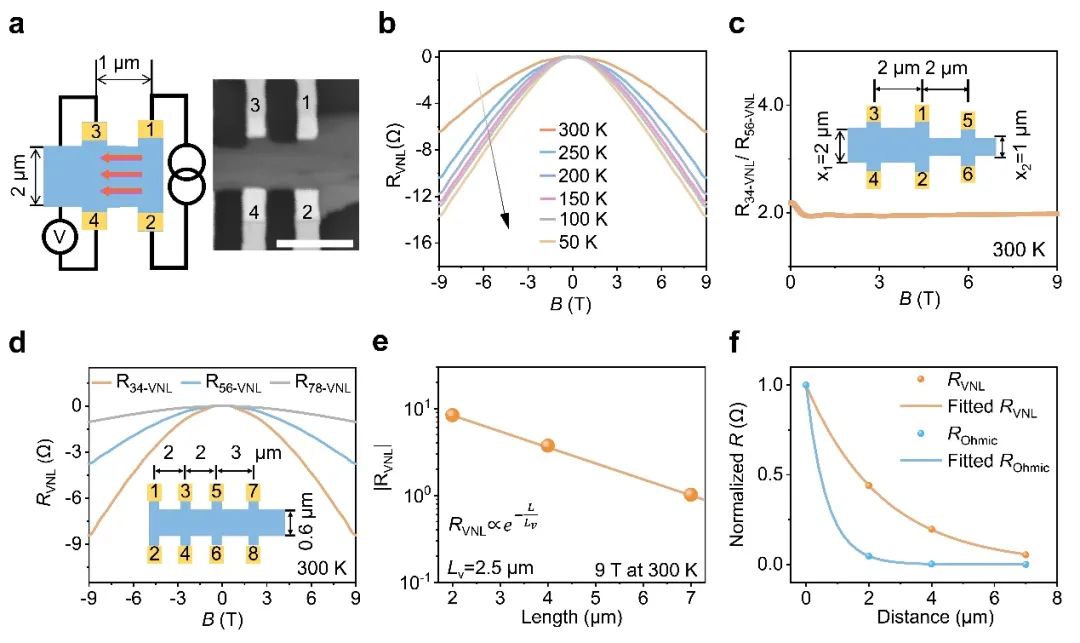

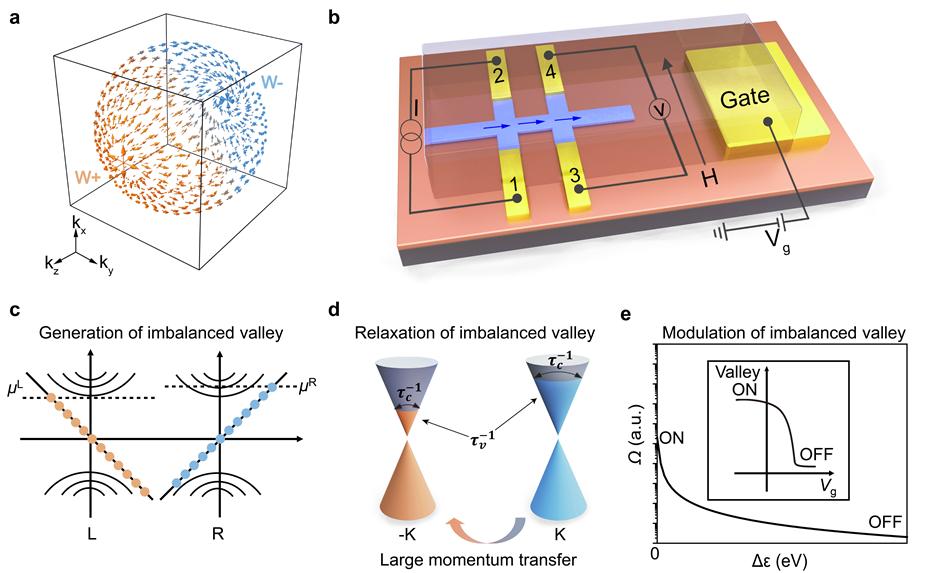

图1 基于外尔材料的室温谷场效应晶体管。(a) 外尔材料动量空间中的非平庸贝里曲率。(b) 基于外尔半导体的谷场效应晶体管示意图。(c) 在手征反常的作用下,产生不平衡能谷赝自旋。(d) 通过能谷间散射来驰豫赝自旋,需要较大的动量转移。(e) 静电栅压调控(Vg)可以控制费米能级位置和贝里曲率的强度,从而实现晶体管的“开”和“关”态。“H”构型器件(图2a)可以用来检测基于谷信号的非局部电阻。在端口1和2施加恒定电流,在端口3和4测量非局部电压并换算出非局部电阻(RNL)。谷电阻随着温度的升高(50 K增加到300 K)而逐渐降低(图2a)。在室温下,我们仍然可以观察到显著的非局部谷电阻(-6.4 Ω, 9 T),因为谷间散射需要大的动量传递。谷输运特性可以通过宽度和长度相关的非局部谷输运测量得到进一步验证。非局域电阻的比值,接近于器件的宽度比值(图2c);非局域电阻的强度与传输距离有关,距离越长(由2到7微米),信号越弱。但即使在7μm的长传输距离下,仍然可以检测到非局域谷电阻(-1.0 Ω,9T)。图2e显示了谷电阻在半对数曲线中与传输距离的关系,显示出了较好的线性度,可以提取得到2.5μm的谷扩散特征长度,这揭示了Te中谷输运的低损耗传输特性。图2f显示了归一化能谷和常规电荷输运贡献的长度相关性。欧姆电阻随距离的增加呈现快速衰减(由Drude模型描述)。相比之下,谷输运仍然可以在较长距离被检测到,因为谷输运的弛豫过程需要到较大的准动量转移。

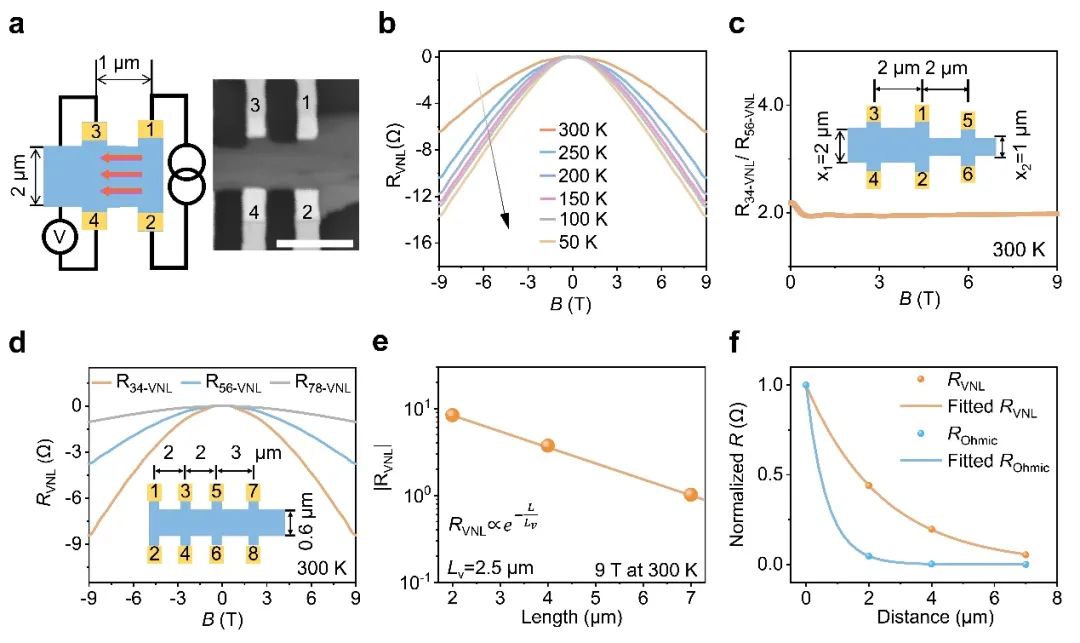

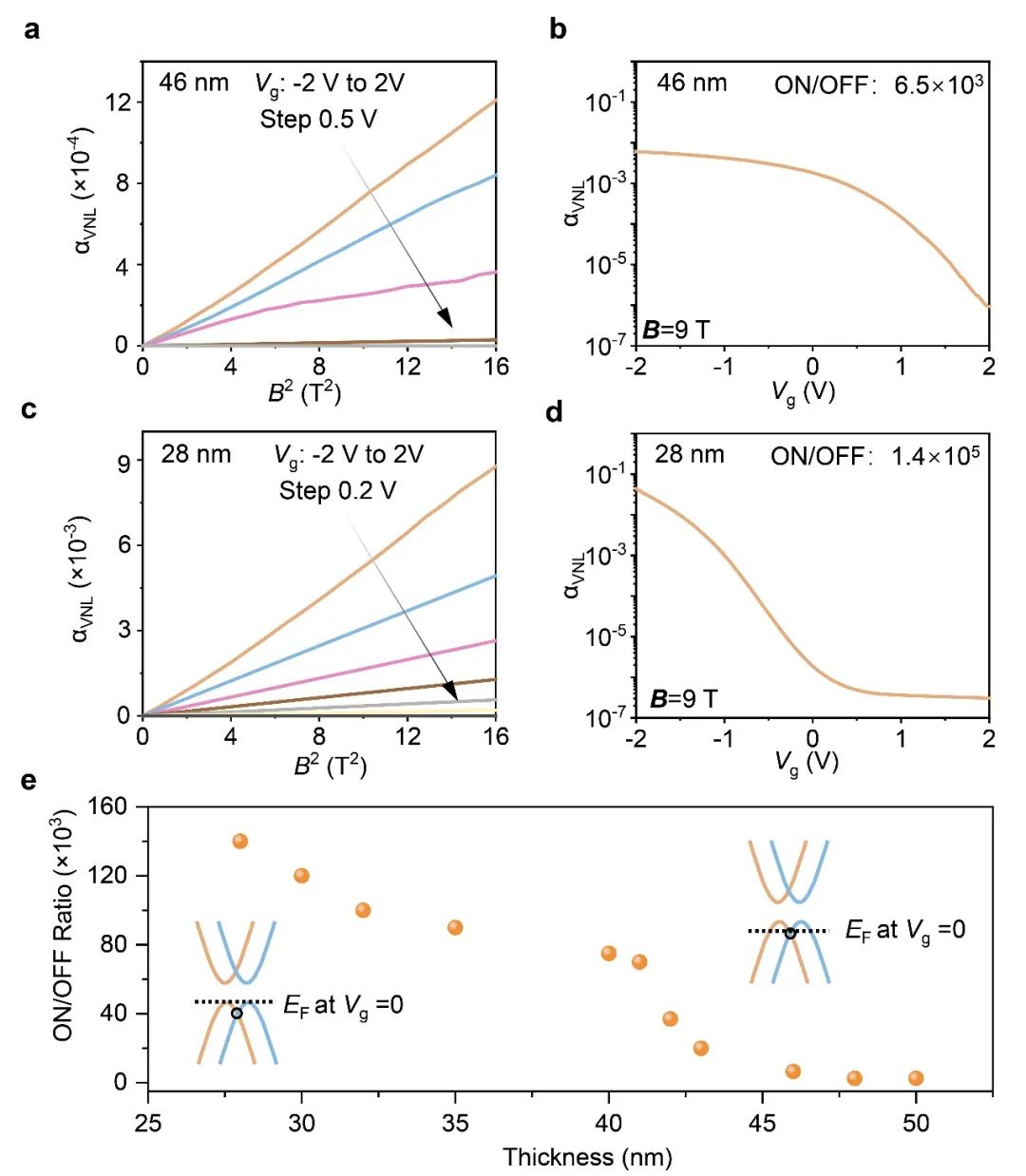

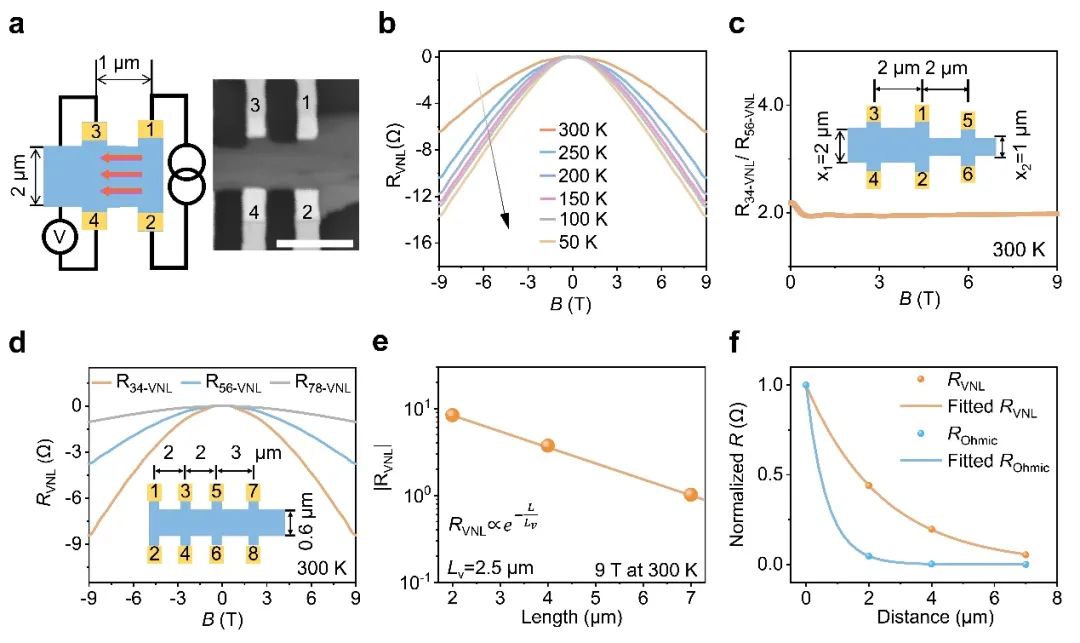

图2 温度、器件宽度和长度相关的能谷输运特性. (a) "H" 构型能器件。端口1和2施加电流,端口3和4进行电压检测。(b) 温度相关的能谷输运特性. (c) 器件宽度相关的能谷输运特性。(d) 器件长相关的能谷输运特性。(e) 在半log图中,室温下RVNL与器件长度 满足线性关系,谷扩散特征长度为2.5微米。(f) 归一化的欧姆/能谷输运—长度曲线。为了在室温下有效地调节贝里曲率和谷电阻的强度,我们采用具有约10μF/cm2等效电容的离子液体(DEME-TFSI)进行静电栅压调控。图3a显示了46 nm厚Te晶体管的输出曲线,对应的转移曲线具有103的开/关比(图3b)。对于28nm厚的Te薄片,其在从-2V到2V的栅压下,显示出105的开/关比(图3c, d),这与基于电荷输运机制Te 晶体管的开/关比相当(104至106),高于现有文献中谷晶体管的开/关比(102至103)。图3e总结了了谷晶体管中Te厚度与开关比的关系。随着Te薄片厚度从28nm增加到50nm,Te谷器件下的开/关比从1.4×105降低到2.6×103,因为Te厚样品本身的载流子浓度较高,调节费米能级位置更困难。

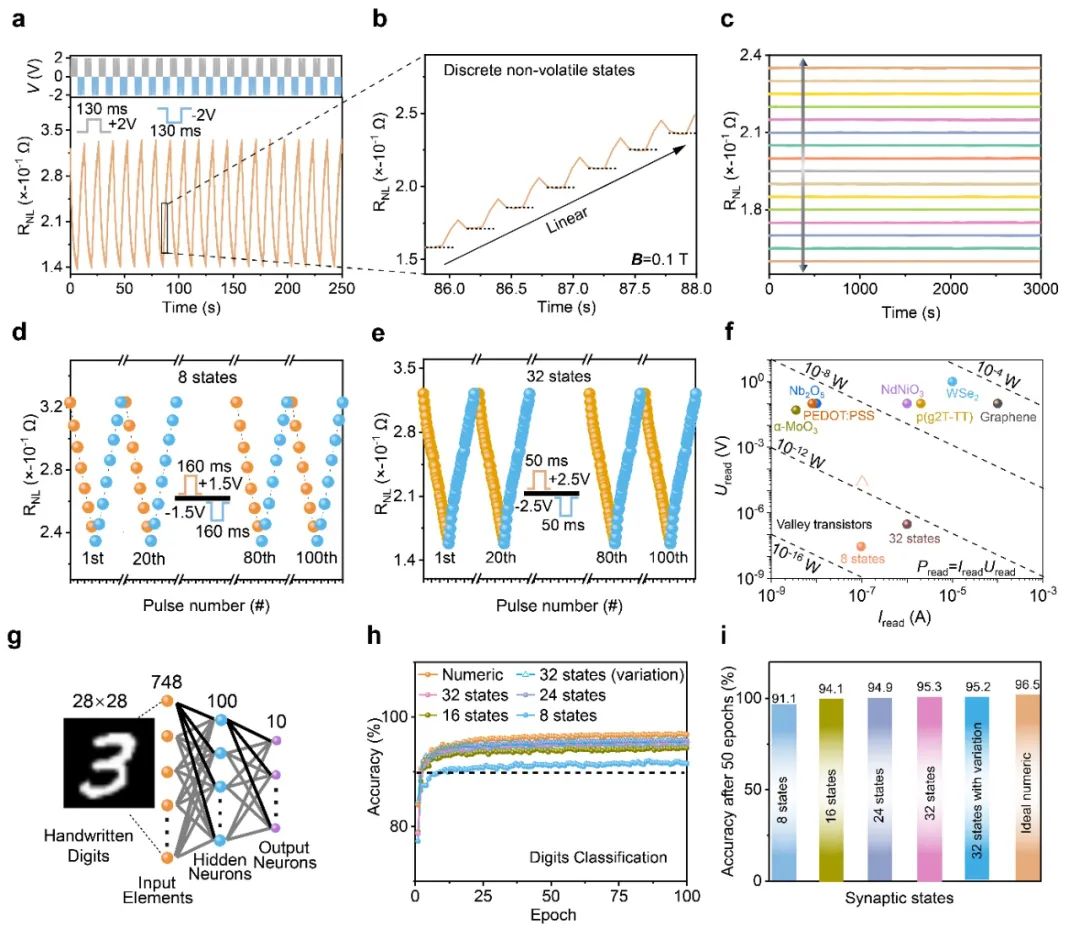

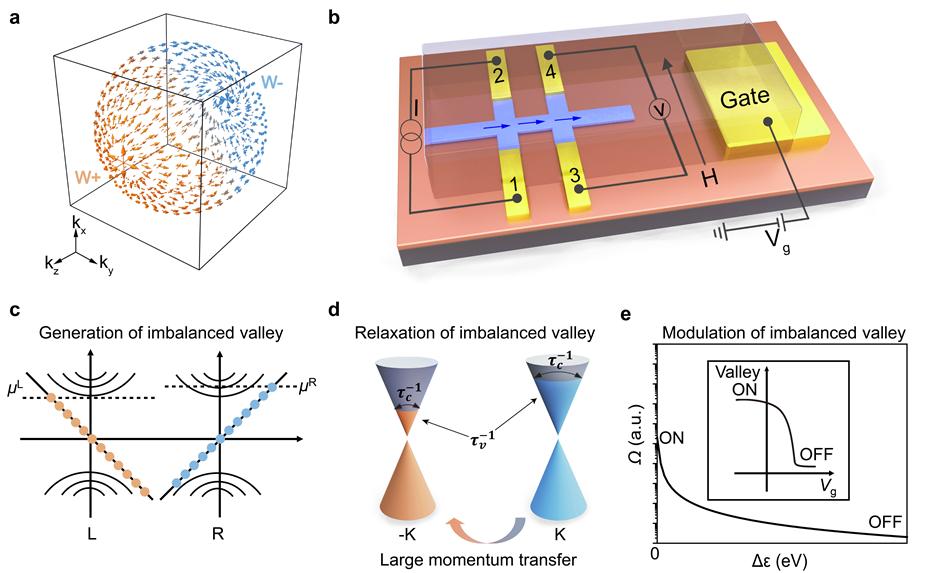

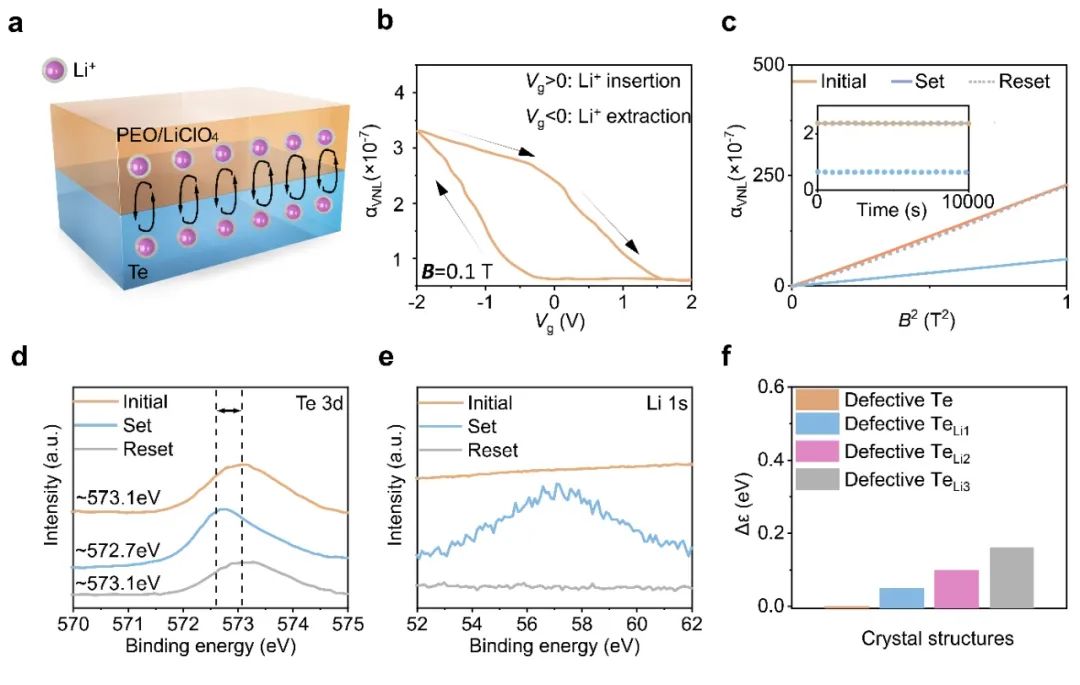

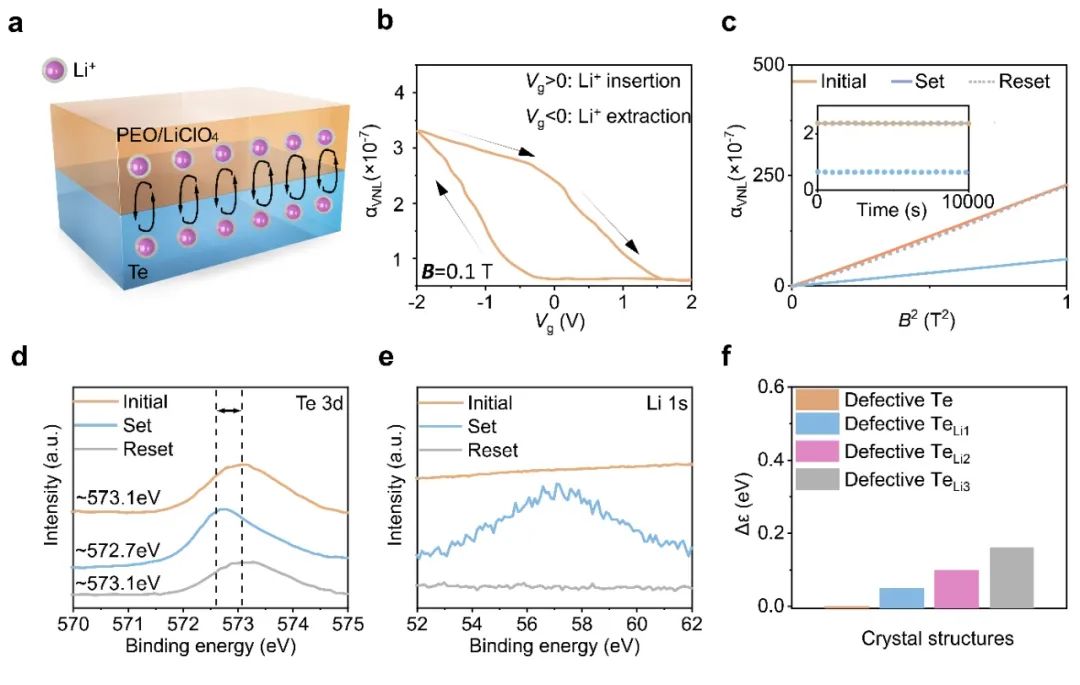

图3 在室温下工作的易失性谷晶体管。(a, b) 46 nm厚Te器件的输出和转移特性曲线。(c, d) 28 nm厚Te器件的输出和转移特性曲线。(e) 基于不同厚度Te的谷场效应晶体管开关比。我们采用稳定的固态电解质PEO/LiClO4来实非易失性谷晶体管(图4a)。锂离子可以在正栅压下插入Te薄片中,并在负栅极电压下脱出。锂离子的插入和脱出可以使费米能级非易失性升变化,从而影响贝里曲率与晶体管的输出信号(图4b)。图4c显示了栅压施加前后不同状态的输出曲线。施加+2V栅压并持续1s后,谷电阻降低并保持。随后施加-2V栅压并持续1s后,谷电阻接近初始状态并保持,这表明我们可以实现可逆的离子插入/提取。为了验证Li+插入/提取的工作机制,我们进行了系统的XPS测试(图4d,e)和密度泛函理论计算(图4f),表征结果和计算数据与晶体管测试结果是一致的。

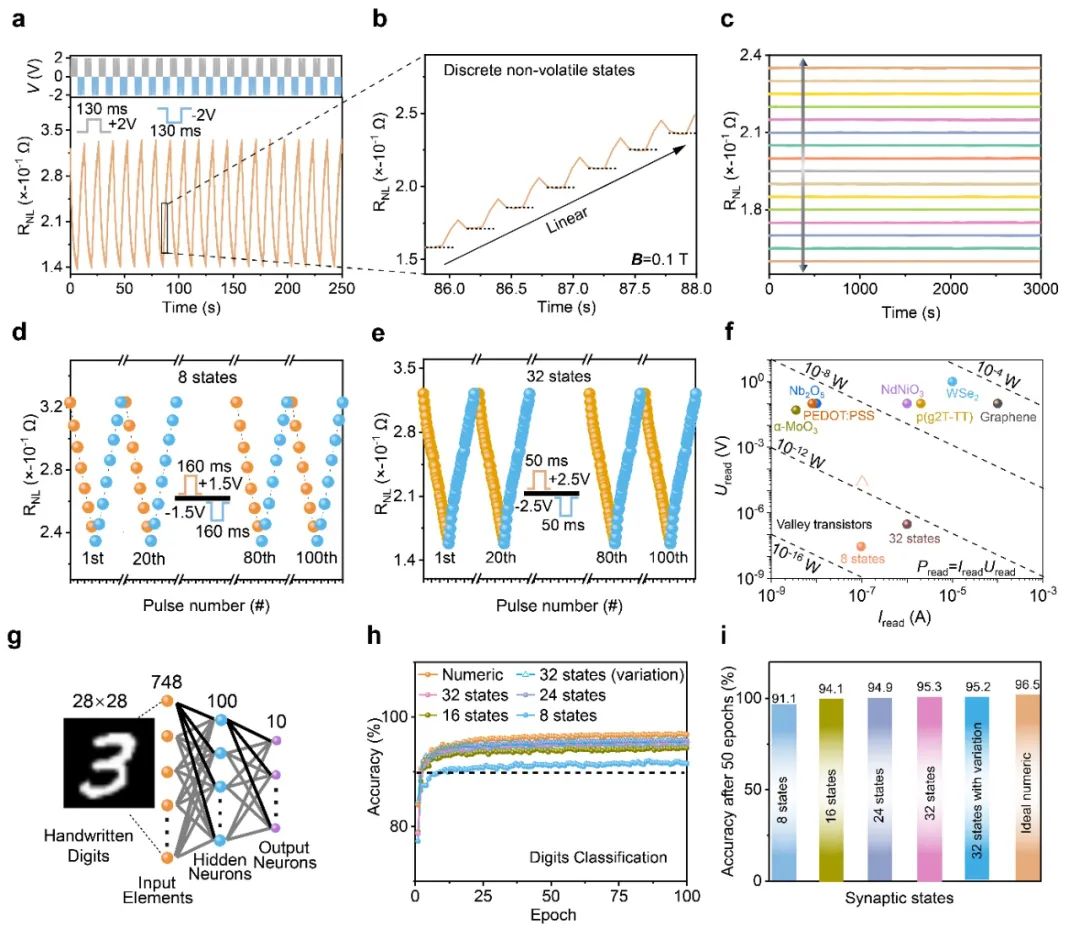

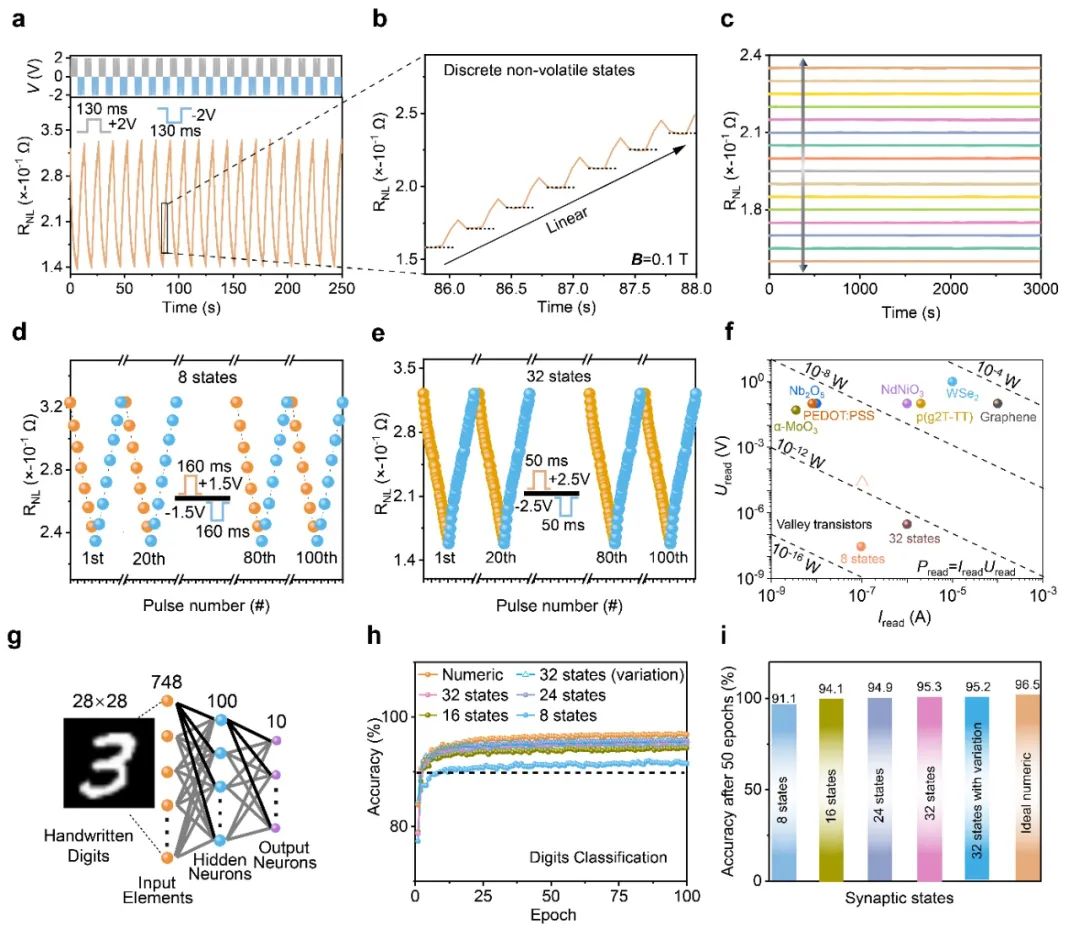

图4 在室温下工作的非易失性谷晶体管。(a) 基于Li+可逆脱嵌来实现非易失性谷晶体管。(b) 具有较大回滞的转移曲线. (c)不同状态下的输出曲线. 利用+2 V 栅压来实现高输出值态(set),-2 V 栅压来实现低输出值态(reset)。(d) Te的XPS 3d 谱。(e) XPS Li 1s谱.(f) 在不同构型中,费米能级与外尔点的距离。含缺陷的 Te (1.23% Te 缺陷浓度), 含缺陷和锂离子嵌入的 TeLi1 (1.23% Te 缺陷浓度和1.23%锂掺杂浓度), TeLi2 (1.23% Te 缺陷浓度和2.46% 锂掺杂浓度) 和 TeLi3 (1.23% Te 缺陷浓度和3.69% 锂掺杂浓度。.神经网络的训练需要可编程的非易失性态和权重更新。非易失性谷晶体管可以模拟突触功能(图5)。通过向谷晶体管的栅极施加写入电压脉冲(+2V/-2V,130ms),该器件展示了20种不同状态的谷输出信号(图5a),对应于长期抑制和长期增强突触行为。在负栅压的作用下,器件展示出了高线性度的多个稳定上升态(图5b),因为离子的脱出使得费米能级位置下移并靠近外尔点。所制备器件的输出的多个状态阻值,3000 s内保持基本稳定(图5c)。在循环稳定性测试中,8个(图5d)和32个(图5e)状态下,器件的输出值保持稳定,且具有很高的线性度。由于谷传输不受到低能散射的影响,我们能够使用相对低的电流(100 nA)和电压(10 nV)进行读出,同时保持高信噪比。图5f将读出电压、读出电流和读出功率与文献工作进行了比较。我们的工作在读出过程中显示出低功耗(欧姆贡献为~pW,谷贡献为~fW),比传统基于电荷的突触器件低几个数量级(推理过程中读出功率为nW至μW水平的)。基于谷突触晶体管的三层神经网络,我们对手写数据库进行分类(图5g)。随着非易失性态从8增加到32,分类精度逐渐提高(图5h)。在8种态下,具有超低的非线性(0.012/-0.442),识别精度高于91%;在32个状态下,准确度达到95.2%。50个训练期后的分类准确度(图5i)与目前基于电荷输运机制的神经形态计算工作性能相当。

图5 突触特性谷晶体管用于神经网络计算。(a) 基于固态电解质PEO/LiClO4和电压脉冲调控来实现突触的增强和抑制特性。(b)图(a)的放大图。负栅压作用下,实现了具有高线性度的多个稳定态。(c) 在3000 s的测试实验中,谷信号很稳定。正栅压的时候降低输出值,负栅压的时候增加输出值。(d, e) 分别在100 nA和1 μA的恒定电流下,谷晶体管的循环变动特性。(f) 文献和我们工作中读出电流与电压的对比。(g) 人工神经网络用于手写数字分类。(h) 基于非易失性谷晶体管来进行手写数字分类的训练。黑色虚线对应于90%的识别精度. (i) 训练50次后的识别率。

我们基于外尔半导体Te制备了可以在室温工作的谷场效应晶体管。在室温下,能谷信号传播距离超过7 微米。通过静电栅压调控,谷场效应晶体管的开关比达到了105。通过锂离子的嵌入和脱出,实现了费米能级和非平庸贝里曲率的非易失性调节。这实现了具有32个稳定态的突触功能,线性度好且对称性高。用于神经网络计算的时候,其读出功耗很低(欧姆电流贡献只有~pW)比已报道的工作低几个数量级(从nW到μW)。用于笔迹数据分类计算的时候,准确率达到95.2%。通过利用谷自由度的低损耗输运特性,我们的谷晶体管为低功耗神经形态计算提供了新的方案。

柴扬博士是香港理工大学应用物理系教授,香港理工大学理学院副院长,香港物理学会副主席,香港青年科学院院士,IEEE Distinguished Lecturer。获得过香港研究资助局杰出青年学者奖,香港理工大学校长特设杰出成就奖,半导体科学技术早期职业奖,纳米研究青年科学家奖等。担任过IEEE电子器件学会香港分会主席,IEDM技术委员会委员,国家自然科学基金评审专家。[1] Chen, J., Zhou, Y., Yan, J. et al. Room-temperature valley transistors for low-power neuromorphic computing. Nature Communications 13, 7758 (2022)[2] Chen, J., Zhang, T., Wang, J. et al. Topological phase change transistors based on tellurium 外尔 semiconductor. Science Advances 8.23: eabn3837 (2022).[3] Chen, J., Zhang, T., Wang, J. et al. Field-effect chiral anomaly devices with Dirac semimetal. Advanced Functional Materials, 31, 2104192 (2021).