特别说明:本文由学研汇技术 中心原创撰写,旨在分享相关科研知识。因学识有限,难免有所疏漏和错误,请读者批判性阅读,也恳请大方之家批评指正。研究背景

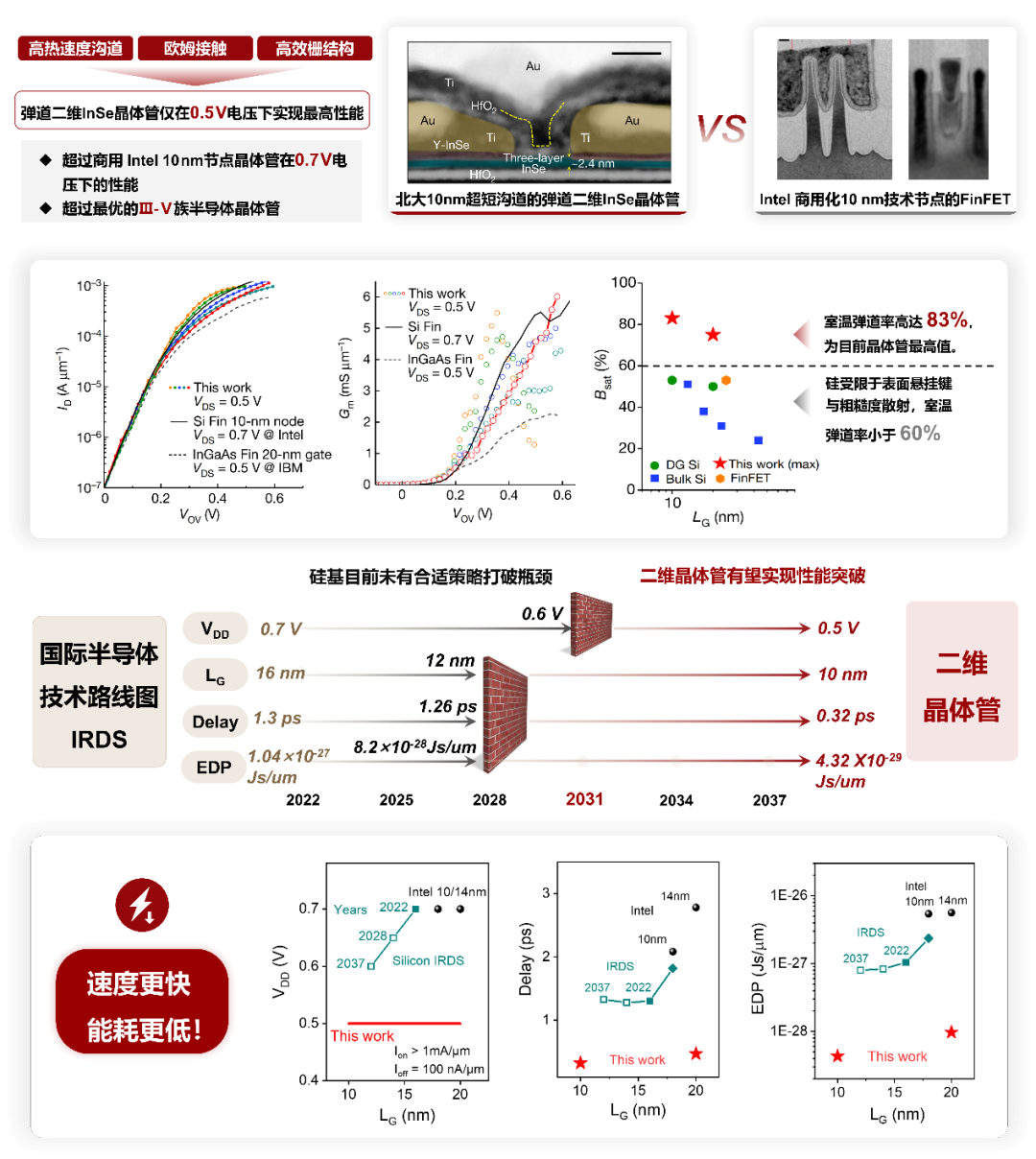

芯片为大数据和人工智能的发展提供源源不断的动力,芯片速度的提升得益于晶体管的微缩,然而当前传统硅基场效应晶体管的性能逐渐接近其本征物理极限。国际半导体器件与系统路线图(The International Roadmap for Devices and Systems, IRDS)预测硅基晶体管的极限栅长将停止在12 nm,工作电压不能小于0.6 V,这定义了未来硅基芯片缩放过程结束时的最终集成度和功耗,因此亟需发展新型沟道材料来延续摩尔定律。

关键问题

原子级厚度的二维半导体因其超薄体和高迁移率的优势,是极具潜力的芯片沟道材料,全球多家领先半导体制造公司与研究机构均对其投入大量研究。但2D半导体和高k介质之间的低质量界面,2D半导体-金属界面上具有相当大肖特基势垒的源极和漏极接触,以及2D半导体固有的缺点限制了其发展。迄今为止所有二维晶体管所实现的性能均不能媲美业界先进硅基晶体管,其实验结果远落后于理论预测,不足以展示二维半导体的最终潜力。

新思路

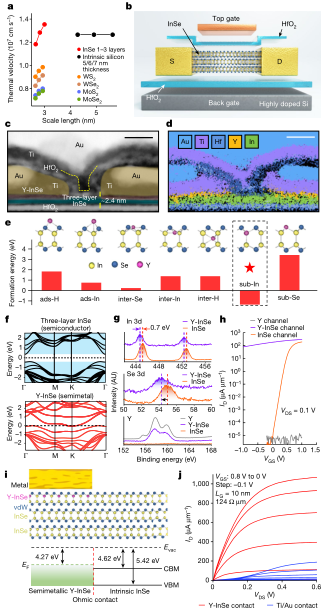

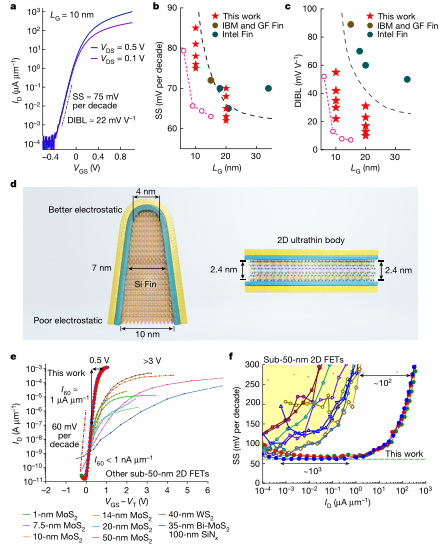

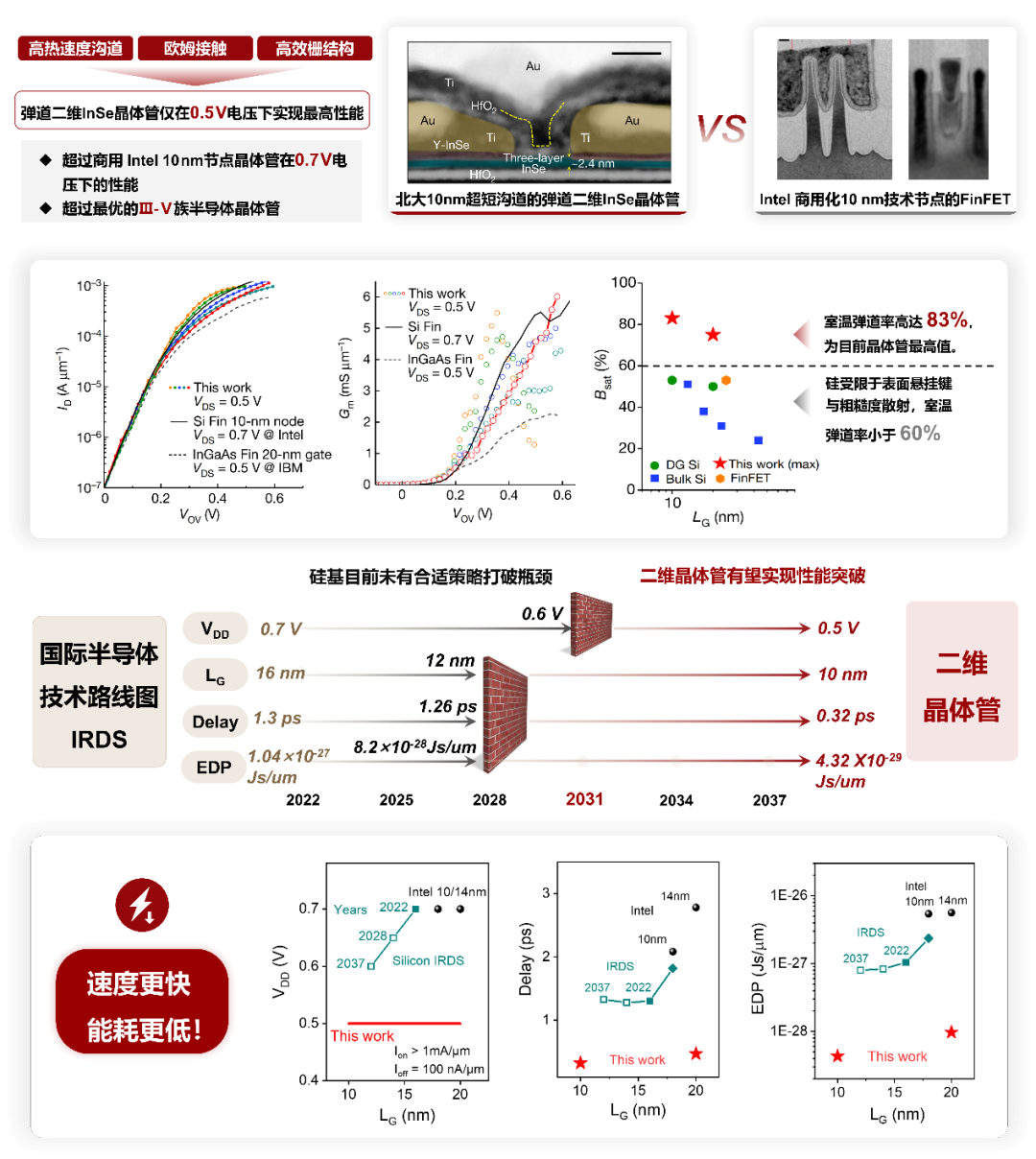

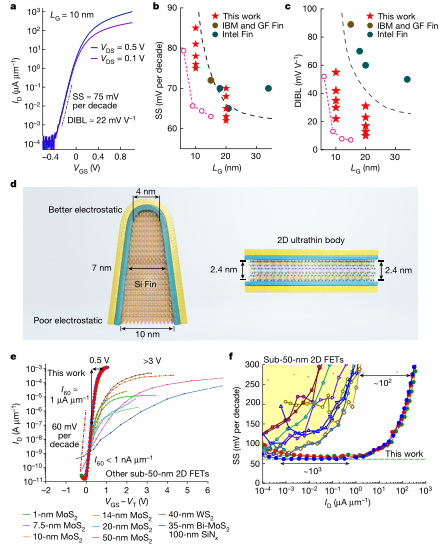

有鉴于此,北京大学电子学院彭练矛教授-邱晨光研究员课题组等人报道了一种以2D硒化铟(InSe)为沟道材料的高热速场效应晶体管,在0.5 V下工作,实现了6 mS μm−1的高跨导和饱和区83%的室温弹道比,超过了任何已报道的硅基场效应晶体管。作者提出了一种掺杂钇诱导的相变方法来实现铟硒场效应晶体管的欧姆接触,同时将硒化铟场效应晶体管的沟道长度缩小到10 nm。该InSe FETs可以有效抑制短通道效应,其低亚阈值摆动(SS)为75 毫伏量程,漏极诱导的势垒降低(DIBL)为22 mV V−1。此外,在10 nm弹道InSe FETs中可靠地提取了62 Ω μm的低接触电阻,导致了更小的内在延迟和更低的能量延迟积(EDP),远低于预测的硅极限,将n型二维半导体晶体管的性能首次推近理论极限。

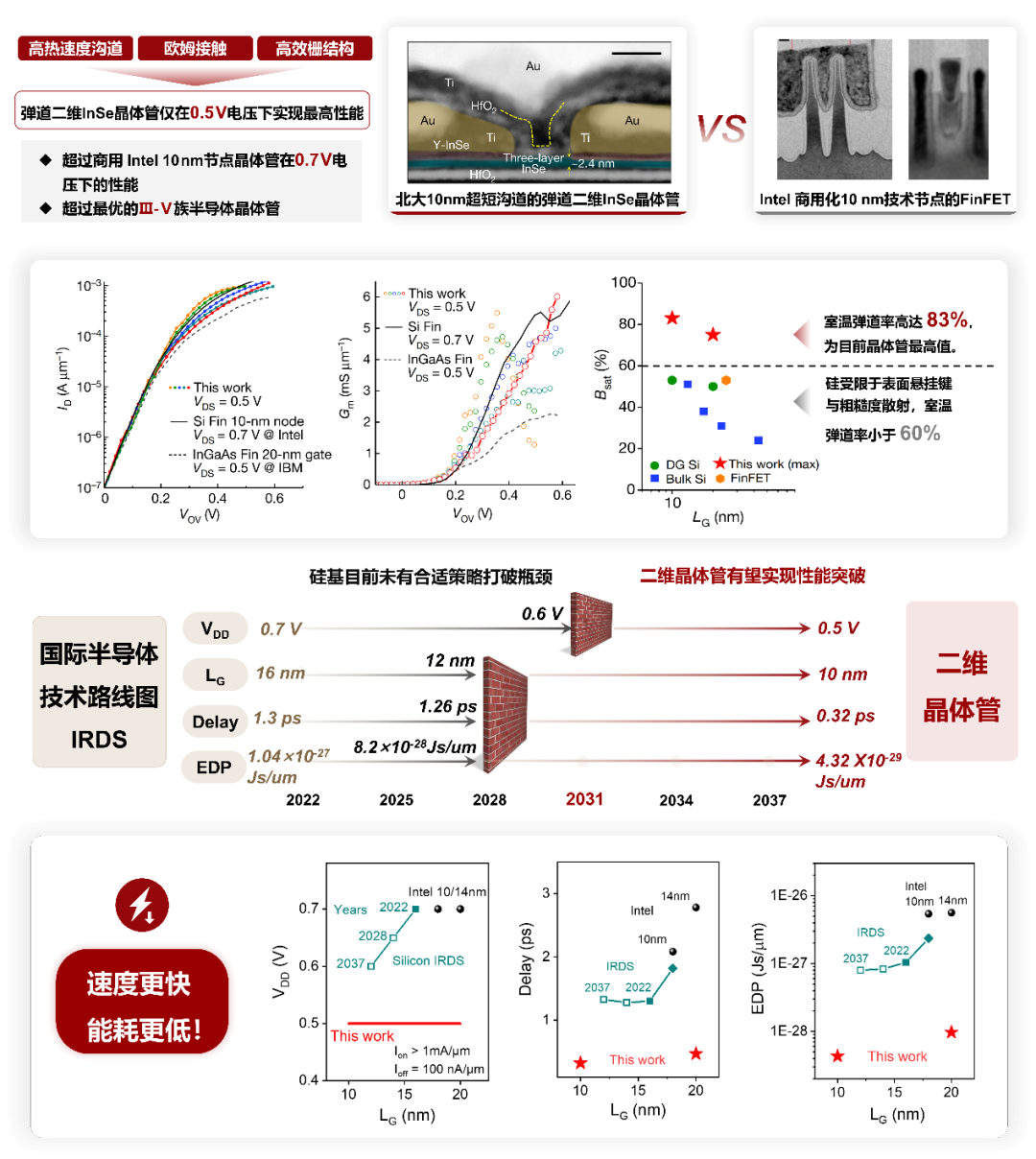

作者构建了三层InSe构建超短弹道晶体管,展示了2D InSe晶体管结构的示意图,并通过钇掺杂将半导体InSe转化为半金属Y-InSe以克服金属电极与二维半导体之间的大接触电阻。作者表明了2D InSe FETs具有高注入速度和优异的欧姆接触,证实了弹道晶体管中实现了欧姆接触,并计算了InSe弹道晶体管接触电阻的量子极限。3、通过与硅基FETs转移特性比较,证实了2D InSe FETs的优越将2D InSe FETs与硅FETs的性能进行比较,证实了2D InSe FETs在饱和电流、导通电流、弹道比、延迟和EDPs等方面的优异性。4、比较了InSe FETs与硅Fin FETs的短通道效应作者比较了InSe FETs与硅fin FETs的短通道效应,结果表明10纳米FETs表现出更好的SS和DIBL。进一步研究结果表明,双栅结构在抑制短通道效应方面比单栅结构有效得多。1、实现的二维半导体晶体管性能首次超越Intel商用10 纳米节点硅基Fin晶体管作者制备了10纳米超短沟道弹道二维硒化铟晶体管,采用高载流子热速度(更小有效质量)的三层硒化铟作沟道,实现了6 mS μm−1的高跨导和饱和区83%的室温弹道比,首次使得二维晶体管实际性能超过硅基Fin晶体管。将二维晶体管的工作电压降到0.5 V,这也是世界上迄今速度最快能耗最低的二维半导体晶体管。本工作解决了二维材料表面生长超薄氧化层的难题,制备出2.6纳米超薄双栅氧化铪,将器件跨导提升到6 毫西•微米,超过所有二维器件一个数量级。作者开创了掺杂诱导二维相变技术,将总电阻刷新至124欧姆•微米,满足集成电路未来节点对晶体管电阻的要求(220欧姆•微米)。沟长缩小到10 nm(超越硅基极限12nm);电压缩小到0.5V (超越2031年硅基极限0.6V);门延时缩减到0.32 ps, 四倍优于硅基极限1.26ps;功耗延迟积缩减到4.32×10-29焦秒/微米,比硅基极限低一个量级。

技术细节

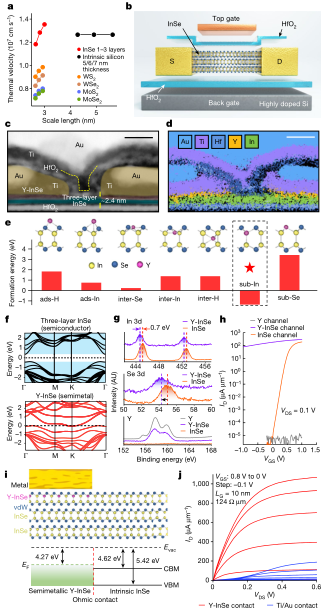

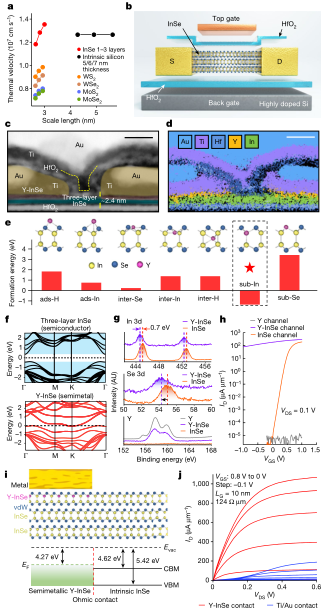

通过参考热速度和自然长度两个关键参数设计具有良好开关特性的超尺度弹道晶体管的基本物理规则。作者使用三层InSe构建超短弹道晶体管,旨在探索2D半导体的终极潜力。作者展示了2D InSe晶体管结构的示意图,确认了二维InSe通道、HfO2介质、电极的位置,以及一层薄薄的钇的存在。为了克服金属电极与二维半导体之间的大接触电阻,作者在接触区采用了一种相变方法,利用钇掺杂将半导体InSe转化为半金属Y-InSe。电传递特性有力地证明了掺杂Y-InSe为通道的场效应晶体管具有半金属性质,栅场调制特别弱(开/关比<10)。使用半金属Y-InSe触点的典型InSe场效应管的总电阻为124 Ω μm,比使用传统Ti/Au触点的总电阻小两个数量级,从而在输出特性方面具有优越的导态性能。

图 弹道InSe FETs的结构和电子特性(图片来源:Nature)与其他报道的2D短通道FETs相比,本工作报道的2D InSe FETs具有高注入速度和优异的欧姆接触,仅需要0.4 V的漏极电压(VDS)就可以使电流饱和并超过1 mA μm−1。欧姆接触弹道10纳米2D InSe FETs在宽温度范围内(300 K至100 K)具有恒定的开态电流,证实了弹道晶体管中实现了欧姆接触。在长通道扩散FETs中,随着温度的升高,沟道内的散射增加,导致开态电流减小, InSe FETs的阈下转移特性中只存在一个单一的热发射区(缺乏热场发射区),证明了在InSe FETs中实现肖特基势垒可忽略的欧姆接触。此外,用郎道尔公式计算了InSe弹道晶体管接触电阻的量子极限。

图 InSe FETs的电子特性及总电阻(图片来源:Nature)为了将2D InSe FETs的性能与硅FETs的性能进行基准测试,直接2D InSe FETs的典型传输特性与10纳米节点硅(英特尔)和20纳米门InGaAs (IBM) fin FETs的传输特性进行比较。具体优势如下:(1). 2D InSe FETs的饱和电流与硅FinFET相当,超过了InGaAs FinFET。在2D InSe FETs中实现了6 mS μm−1 (0.5 V)的记录峰值跨导,这是所有报道的低维纳米材料FETs的最高值,与Si 10纳米节点FinFET(英特尔)相当,但电压较低0.5 V(硅为0.7 V),比InGaAs FinFET (IBM)大三倍。(2). 在VDD=0.5 V的超低电压下,2D InSe FETs导通电流范围为0.7~1.2 mA μm−1,跨导范围为3 ~ 6ms μm−1,比其他2D FETs大大约一个数量级。(3). 2D FETs饱和区域的室温弹道比被提取出来,达到了83%以上,这是迄今为止所有2D晶体管的最高记录值,超过了之前报道的所有硅FETs。(4). InSe FETs的VDD被缩小到0.5 V,仍能够切换通道,电流从100 nA μm−1(关闭状态)到超过1 mA μm−1(打开状态),这对于Si single-sheet MOS FET是不可能的。(5). InSe FETs在延迟和EDPs(无重叠结构)方面比硅fet表现出更好的缩放趋势。最佳10nm栅长InSe场效应晶体管的延迟为0.32 ps和0.87 ps,这比IRDS 2022预测的Si场效应晶体管的最终延迟要好。(6). 10 nm栅长InSe FETs的EDPs低至4.32 × 10−29 Js μm−1和3.20 × 10−28 Js μm−1,远小于Si FETs的预测极限。

图 对标InSe,硅和InGaAs FETs(图片来源:Nature)

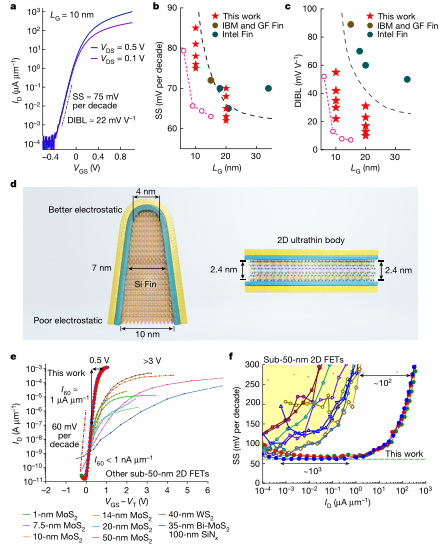

图 弹道二维硒化铟晶体管与先进节点硅基晶体管的比较(图片来源:北京大学)10纳米InSe FET的典型传输特性显示了理想的开关行为,包括75 毫伏量程的SS, 22 mV V−1的DIBL和超过7个数量级的电流开/关比。10nm InSe场效应晶体管的离态泄漏电流小于1nA μm−1,满足商用标准性能IC的要求。将InSe FETs的SS和DIBL的标度趋势与最先进的硅FETs的理论模拟进行了比较。结果表明10纳米FETs表现出更好的SS和DIBL。均匀厚度为2.4 nm的三层2D InSe通道表现出远低于50 mV V−1的DIBL。模拟预测,通过将2D沟道从三层细化为单层,10nm栅长2D FETs的SS可以进一步降低到65 毫伏量程, DIBL可以进一步降低到17mV V−1,为进一步优化off-state泄漏电流提供了足够的空间。进一步研究结果表明,双栅结构在抑制短通道效应方面比单栅结构有效得多。与其他报道的2D FETs相比,该弹道InSe FETs在更大的电流量级下具有更陡的SS。欧姆接触的实现不仅有助于大的导通电流和大的跨导,而且是在近阈值区域实现理想开关特性的一个容易被忽视的先决条件。

图 InSe FETs与硅fin FETs的短沟道效应比较(图片来源:Nature)

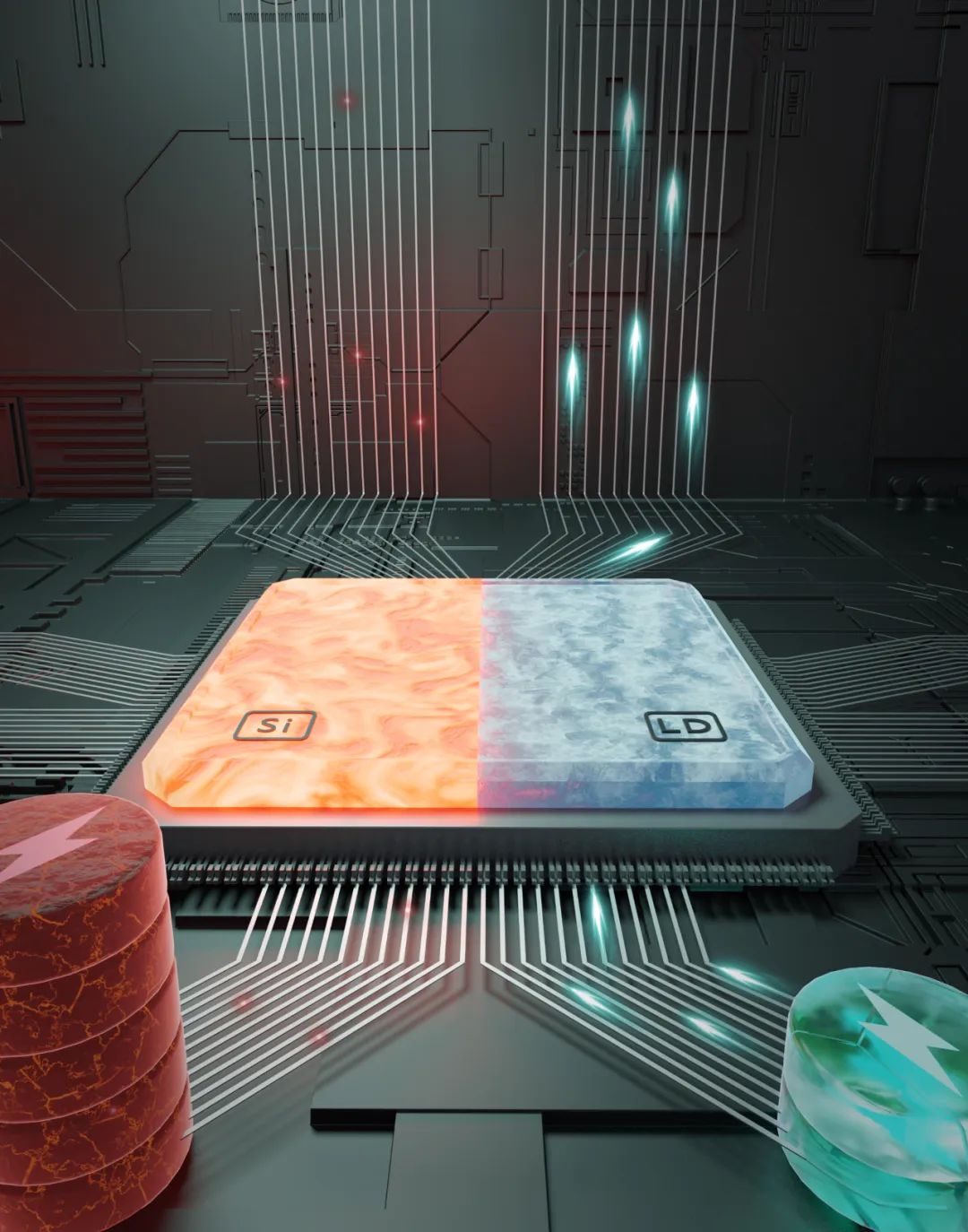

图 展望:更快更省电的低维半导体芯片(图片来源:北京大学)

展望

总之,本工作表明已经制造出具有欧姆接触、高栅极效率和接近理想弹道比的超尺寸高性能InSe FETs,首次证实了2D FETs可以提供接近理论预测的实际性能,是未来Å节点上硅FETs的强大竞争对手。这项工作突破了长期以来阻碍二维电子学发展的关键科学瓶颈,将n型二维半导体晶体管的性能首次推近理论极限,率先在实验上证明出二维器件性能和功耗上优于先进硅基技术,为推动二维半导体技术的发展注入强有力的信心和活力。Jianfeng Jiang, et al. Ballistic two-dimensional InSe transistors. Nature, 2023.DOI:10.1038/s41586-023-05819-w

彭练矛教授

中国科学院院士,北京大学电子学院院长。1994年获首批国家杰出青年科学基金资助,1999年入选首届教育部“长江学者奖励计划”特聘教授。长期从事碳基电子学领域的研究,做出一系列基础性和开拓性贡献。四次担任国家“973计划”、重大科学研究计划和重点研发计划项目首席科学家。在《科学》《自然》等期刊发表SCI论文400余篇。相关成果获国家自然科学二等奖(2010和2016年)、高等学校科学研究优秀成果奖(科学技术)自然科学一等奖(2013年)、北京市科学技术一等奖(2004年),入选中国科学十大进展(2011年)、中国高等学校十大科技进展(2000和2017年)、中国基础科学研究十大新闻(2000年)。个人获何梁何利基金科学与技术进步奖(2018年)、全国创新争先奖(2017年)、推动“北京创造”的十大科技人物(2015年)、全国优秀博士学位论文指导教师(2009年)、北京大学首届十佳导师(2013年)等荣誉。

邱晨光研究员

北京大学电子学院研究员,“博雅青年学者”。国家基金委“优青”(2021)、国家重点研发计划青年首席科学家(2021)、KJW 173 JCJQ 首席科学家(2022)。从事纳米电子器件方面研究,在Nature, Science, Nature Electronics, Nature Nanotechnology, ACS Nano, Nano Letters, IEDM等顶级国际期刊和会议上发表论文; 以第一作者和通讯作者在《科学》上发表论文两篇,在《自然》上发表论文一篇。Science论文“5纳米栅长碳纳米管晶体管”实现了晶体管开关的量子极限,入选ESI高被引用论文和热点论文,入选2017年中国高校十大科技进展,2017年中国100篇国际高影响论文。Science论文“狄拉克冷源晶体管”首次在国际上提出并实现冷源亚60超低功耗新器件机制,拓宽了超低功耗器件领域范围,入选2018全国科创中心重大标志性原创成果。Nature论文“弹道InSe晶体管”研制出世界上迄今弹道率最高、速度最快、功耗最低的二维晶体管,性能超过硅基极限。

北京大学电子学院博士研究生,师从彭练矛教授与邱晨光研究员。从事二维电子器件的极限性能的探索与器件物理研究,致力于开发超越硅基极限的后摩尔新型电子技术。在Nature,Nano Letters等国际知名杂志上以第一作者身份发表论文九篇,博士期间针对二维电子学领域的关键科学瓶颈和底层科学问题进行攻关,实现了近弹道输运的高速二维晶体管,性能和功耗均优于商用硅基先进技术节点。曾获省级优秀毕业生、研究生“校长奖”、研究生国家奖学金等荣誉。香港大学研究助理教授。2020年于北京大学信息科学技术学院取得理学博士学位。从事后摩尔未来节点纳米器件结构和物理研究,以及锂离子电池电化学模型研发。在Nature,Science,Nature Electronics,Nature Communication,Science Advance,IEEE Transactions on Electron Device,Applied Physics Letters,IEDM等国际知名杂志和会议上发表学术成果四十余篇。系统研究了低维材料器件的建模方法,包括紧凑模型、TCAD数值模拟及基于密度泛函的第一性原理计算。利用紧凑模型首次研究顶栅碳纳米管器件弹道率,在理论上证明了狄拉克源具有跨导增强的特性,利用TCAD数值模拟设计新型抑制双极性输运器件结构,基于第一性原理系统研究了二维材料的去钉扎欧姆接触和器件性能极限等若干关键科学问题,专注于探索后摩尔先进节点器件的底层物理。课题组常年招收博士后与博士生,欢迎有微电子,电子,物理,化学,材料背景的有志之士加入课题组。可直接联系邱晨光研究员(email:chenguangqiu@pku.edu.cn)投递简历