特别说明:本文由学研汇技术中心原创撰写,旨在分享相关科研知识。因学识有限,难免有所疏漏和错误,请读者批判性阅读,也恳请大方之家批评指正。

原创丨彤心未泯(学研汇 技术中心)

编辑丨风云

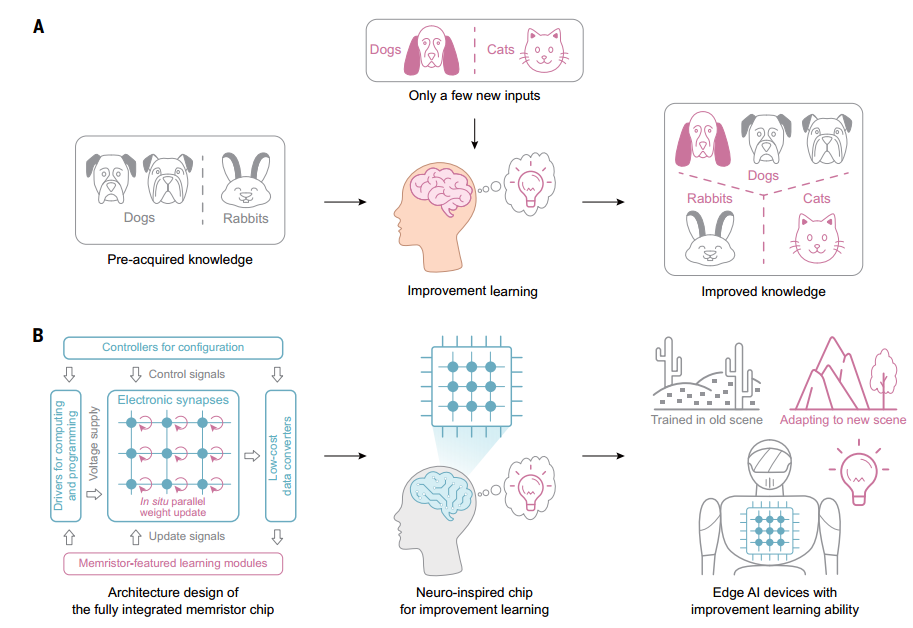

学习对于边缘智能设备适应不同的应用场景和用户来说非常重要。当前训练神经网络的技术需要在计算和存储单元之间移动大量数据,这阻碍了在边缘设备上实现学习。相比之下,基于忆阻器的神经启发计算通过其颠覆性的内存计算架构和模拟计算范式消除了这种广泛的数据移动。

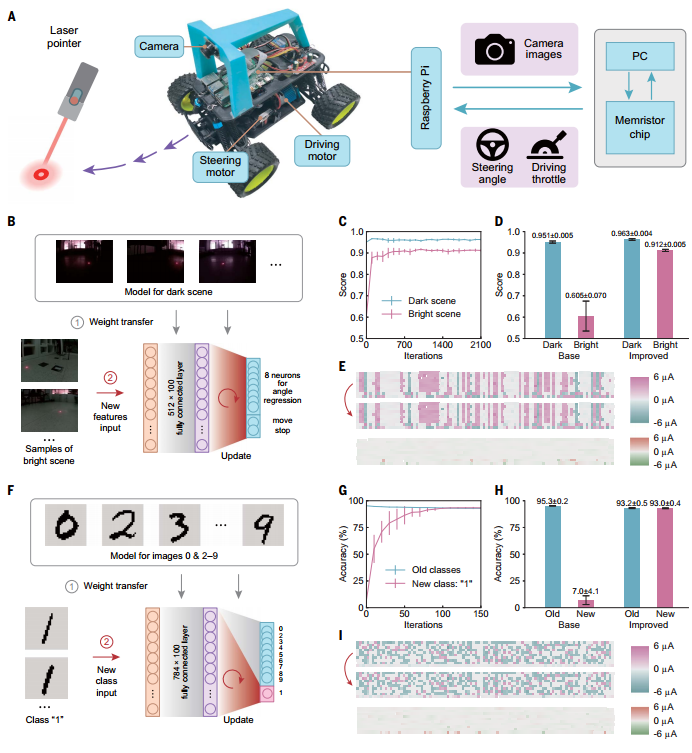

有鉴于此,清华大学吴华强、高滨等人开发了一种具有改进的学习能力和低能耗的全集成忆阻器芯片,提出了基于忆阻器的符号和阈值学习(STELLAR)架构。 STELLAR架构中包括其学习算法、硬件实现和并行电导调谐方案,都是通过使用忆阻器交叉阵列来促进片上学习的通用方法,而不考虑忆阻器器件的类型。所制造的神经启发计算芯片集成了两个忆阻器交叉阵列(总共约160000个单元)和所有必要的电路模块。根据获得的硬件测量结果,忆阻器芯片的能耗比基于数字加速器的系统低35倍。作者演示了多项改进学习任务,包括运动控制、图像分类和音频识别。基于忆阻器的神经计算芯片可以促进边缘人工智能设备的开发,以适应新的场景和用户。

边缘学习

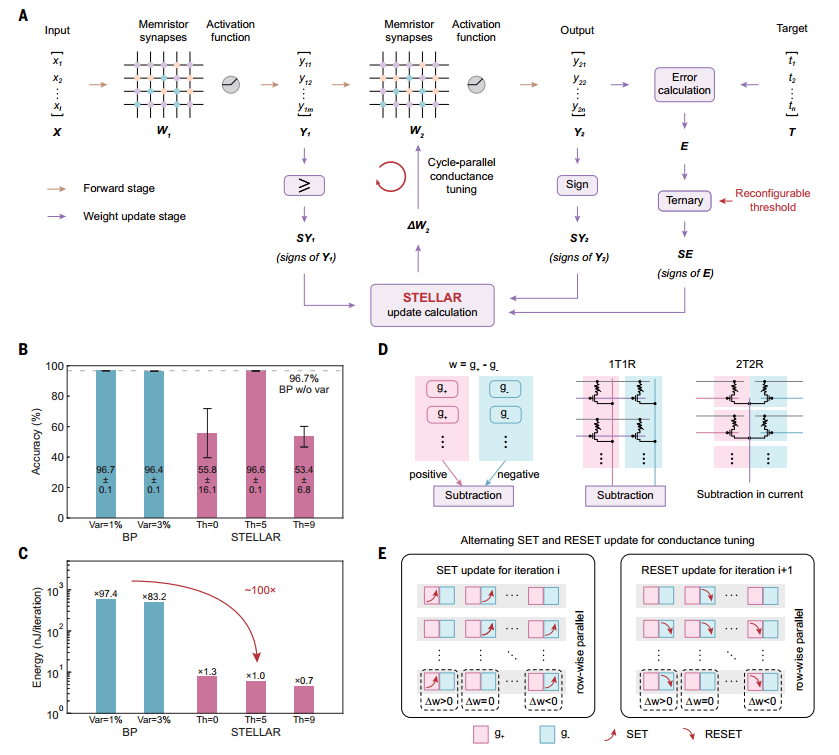

作者展示了一种基于忆阻器的神经启发计算芯片,该芯片能够实现完全学习,并为此提出了基于忆阻器的符号和阈值学习(STELLAR)架构。在该架构中,首先提出了芯片内更新方案来调整忆阻器,节省了电导调谐操作中过多的写入和读取成本。其次,芯片内计算模块旨在确定权重更新方向,该过程仅涉及输入、输出和误差的符号,而不涉及其高精度格式。第三,提出了循环并行电导调谐方案,该方案进一步减少了引起的能耗和延迟,并适应了忆阻器的有限耐用性。

图 使用受神经启发的忆阻器芯片进行边缘学习

用于芯片内学习的忆阻器架构

作者提出了STELLAR架构以可观的能源效率、面积效率和准确性支持芯片内的学习。通过该方案可以避免复杂的精确权值更新计算和写入验证过程以及复杂的外围电路设计,从而实现节能的硬件。在保持几乎相同的精度的情况下, STELLAR架构的能耗比传统BP方法低了两个数量级。此外,作者还提出了一种循环并行电导调谐方案,由于在每次芯片内学习迭代期间仅更新一半的忆阻器器件,循环并行电导调谐方案减少了感应能耗并减轻了对忆阻器耐久性的要求。

图 用于芯片学习的忆阻器架构设计

芯片设计、制造和测量

作者详细展示了STELLAR 架构的整体电路实现和所制造芯片的显微照片。忆阻器器件使用TiN/HfOx/TaOy/TiN材料堆叠,并且制造工艺与标准CMOS工艺兼容。因此,忆阻器可以方便地与复杂的CMOS电路集成,以产生出色的收率(所有160000个单元几乎100%)。作者评估了电导波动对芯片精度的影响,表明了芯片的稳定性。还演示了忆阻器芯片的实时手写数字识别和MNIST图像分类,证实了该芯片的学习能力。然后,利用硬件测量结果评估了芯片内学习的能耗,表明通过优化 ADC 设计可以进一步降低能耗。

图 用于芯片学习的忆阻器芯片

芯片内改进学习

作者利用忆阻器芯片进一步演示了四个改进学习任务,包括学习新样本的运动控制任务、音频识别任务、图像分类任务和新类别的运动控制任务。结果表明,只需少量新输入即可快速实现新知识的学习,且这种学习是在不丢失预先获得的知识的情况下完成的。所提出的 STELLAR 架构可以扩展到更大的神经网络,并且可以实现具有高精度软件精度的高效改进学习。

图 忆阻器芯片的改进学习演示

参考文献:

WENBIN ZHANG, et al. Edge learning using a fully integrated neuro-inspired memristor chip. Science, 2023, 381(6663):1205-1211.

DOI: 10.1126/science.ade3483

https://www.science.org/doi/full/10.1126/science.ade3483