特别说明:本文由米测技术中心原创撰写,旨在分享相关科研知识。因学识有限,难免有所疏漏和错误,请读者批判性阅读,也恳请大方之家批评指正。

原创丨彤心未泯(米测 技术中心)

编辑丨风云

在半导体领域,3D集成不仅能够在单位面积上封装更多器件(“多摩尔”),而且还为“超摩尔”技术引入了多功能性。尽管硅基3D集成电路已投入商业使用,但新兴纳米材料的3D集成仍需进一步发展,基于全2D的单片3D集成尚未大规模实现。

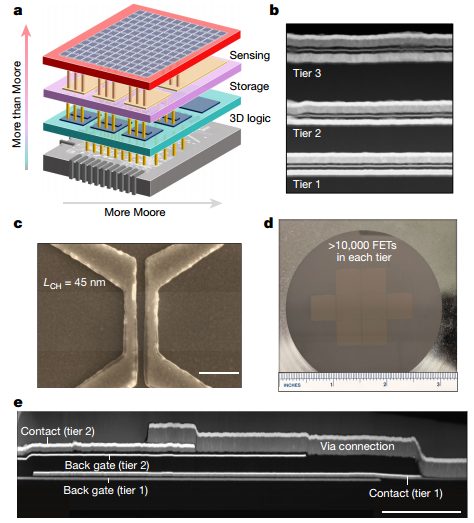

有鉴于此,宾夕法尼亚州立大学Darsith Jayachandran、Rahul Pendurthi和Saptarshi Das等人展示了基于大面积生长的MoS2和WSe2的多功能2D FET的单片3D集成。本文的主要贡献有以下4点:(1)MoS2 FET 晶圆级单片两层3D集成,每层超过10,000个器件;(2) MoS2和WSe2 FET的三层3D集成,第1层和第2层各有800个器件,第3层有450个器件;(3) 每层超过200个按比例缩放的MoS2 FET的两层3D集成,沟道长度LCH=45 nm;(4)实现了基于MoS2的3D电路演示,包括传感和存储。本工作是三层3D芯片以及基于大面积生长2D材料的晶圆级3D集成的首次演示。

2D FET的3D集成

本研究中使用的MoS2和WSe2薄膜是使用金属有机化学气相沉积外延生长的,所有3D集成电路的制造都是在285 nm SiO2/p++-Si 基板上实现的。该衬底仅用作载体衬底,并且原则上可以使用任何其他光刻兼容衬底。作者展示了3D集成堆叠的通用制造工艺流程和堆叠示意图,每层器件均使用层间电介质(ILD)(Al2O3)与其他层进行电气隔离。

图 2D FET的单片3D集成

MoS2 FET的两层晶圆级3D堆叠

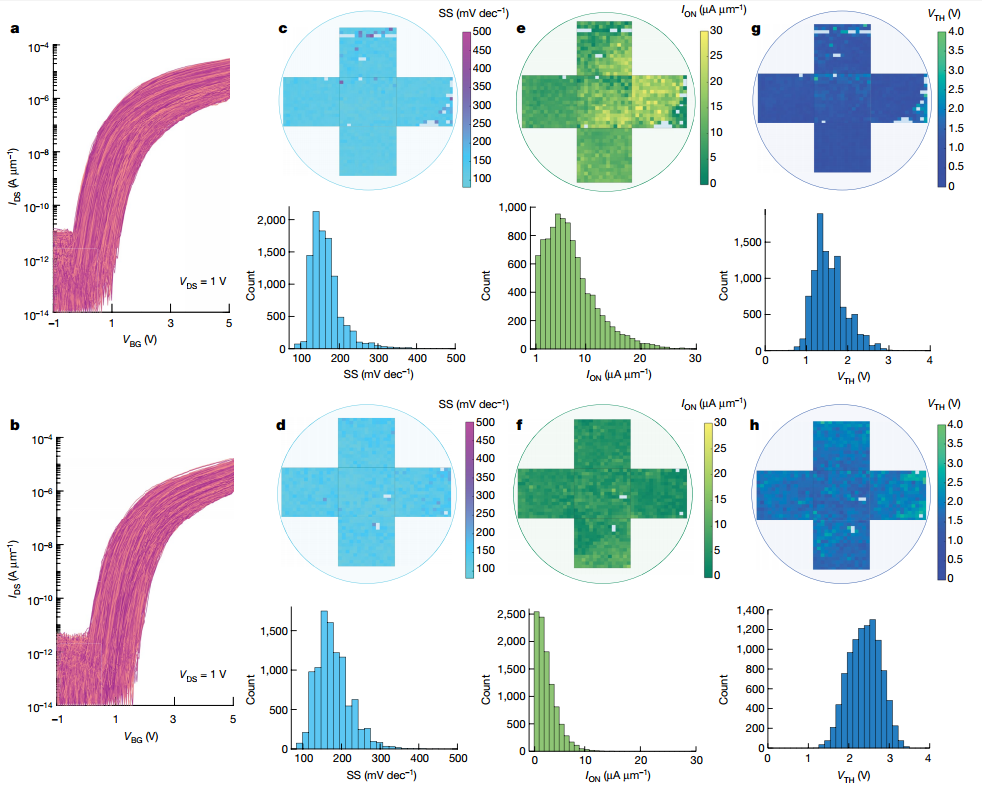

作者按顺序对不同层进行电气表征,制造的晶圆由八个芯片组成,每个芯片的面积为1cm×1cm。每层的器件总数超过30,000 个,对其中的 5 个芯片进行了特征分析。作者展示了了IDS两个数量级变化的亚阈值斜率(SS)的晶圆图和相应的直方图和每层中不同芯片上SS、ION和VTH的传输特性和变化以及相应的直方图,从几个性能指标获得的标准偏差值可以明显看出,两层10,000个2DFET 之间的器件间差异相似,从而增强了3D堆栈制造工艺流程的稳定性。

图 2D FET的晶圆级3D集成

2D FET的三层3D堆叠

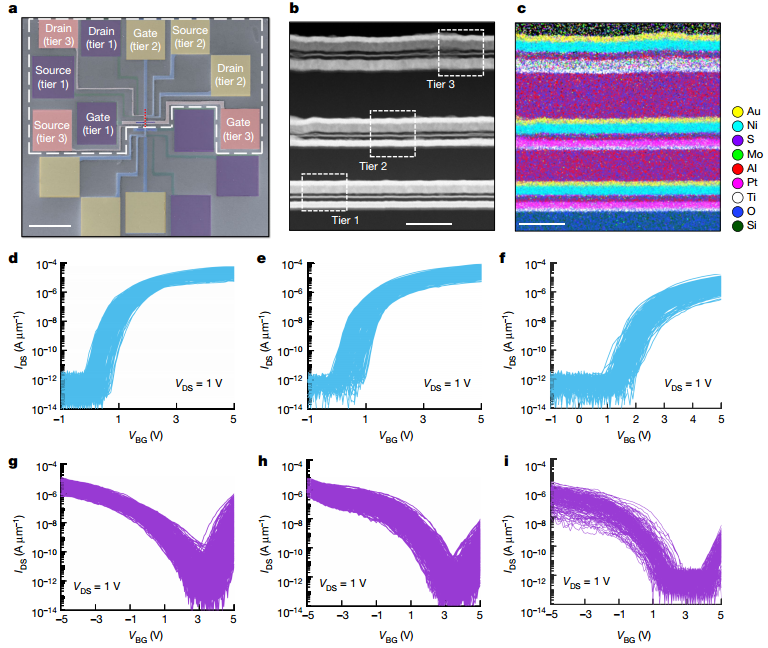

作者通过演示基于MoS2和WSe2的三层3D集成芯片,建立了更高层数的制造工艺流程的稳健性。选择基于MoS2的三层堆叠进行表征,通过SEM-BSE、FIB、HAADF-STEM等多种表征手段证实了所有三层中的MoS2薄膜都是完整的。接下来,对所有三层中MoS2和WSe2 FET的性能进行了统计评估,给出了所有三层的MoS2和 WSe2 的提取性能指标的平均值、中值和标准差值,对于不同的性能指标,根据标准偏差值量化的器件间差异表明,与任何给定层中的 WSe2 FET相比,MoS2 FET之间的差异较小。尽管需要化学机械抛光(CMP)等平坦化技术来制造多层3D集成电路,但这是首次尝试展示基于两种不同材料的2D FET的三层3D集成。

图 2D FET的三层3D集成

两层3D堆叠中的按比例缩放2D FET

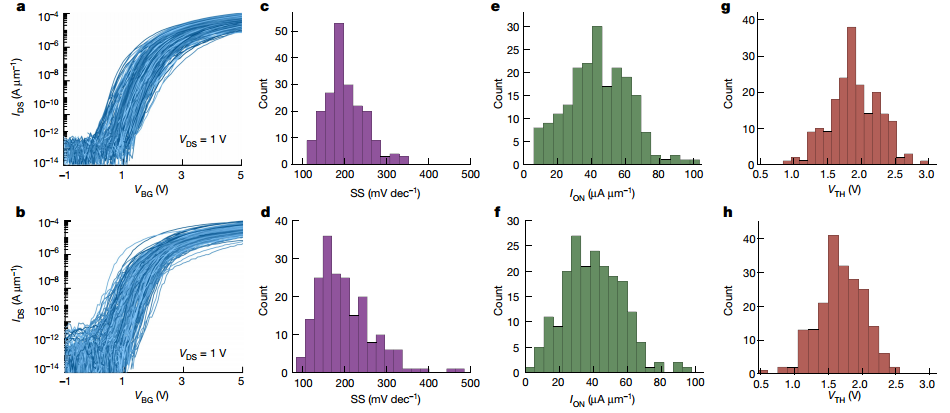

在实现MoS2 FET的两层晶圆级3D集成以及MoS2和WSe2 FET的三层3D 集成后,使用相同的制造流程来制造沟道长度LCH=45 nm和接触长度LC=90nm的两层规模化MoS2 FET。作者展示了第1层和第2层设备性能指标(包括SS、ION和VTH),结果表明缩放器件之间的器件间差异与两层长沟道器件的差异相似,凸显了3D堆叠制造工艺流程的稳健性。此外,作者还演示了将3D集成应用到传感器、存储器和射频器件等非计算系统,探索了MoS2 FET的内存、存储和感光能力。

图 按比例缩小的MoS2 FET的两层3D堆叠

参考文献:

Jayachandran, D., Pendurthi, R., Sadaf, M.U.K. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024).

https://doi.org/10.1038/s41586-023-06860-5